# International Journal of Engineering

Journal Homepage: www.ije.ir

# Design and Qualitative Analysis of Hetero Dielectric Tunnel Field Effect Transistor Device

#### S. Howldar, B. Balaji\*, K. Srinivasa Rao

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Green Fields, Vaddeswaram, Guntur, Andhra Pradesh, India

#### PAPER INFO

Paper history: Received 25 March 2023 Received in revised form 05 April 2023 Accepted 09 April 2023

Keywords: High K Dielectric Materials Tunnel Field Effect Transistor Hafnium Oxide Drain Current Technology Computer Aided Desisn

#### ABSTRACT

A Hetero Dielectric Tunnel field effect transistor with the spacer on both sides of the gate is proposed in this paper. The performance and characteristics of Hetero Dielectric Tunnel field effect transistor using the ATLAS Technology Computer-Aided Design in 5nm regime were analyzed. The band-to-band tunneling leakage current will be reduced by introducing heterojunction and hetero dielectric spacer material in the proposed structure. In Hetero Dielectric Tunnel field effect transistor, double metal gate and high-k dielectric spacer improves high on the current and subtreshold swing. The high-k dielectric Hafnium oxide spacer is placed on both sides of the source and drains to import the tunneling mechanism. The proposed device in the 5nm node has improved DC characteristics such as a High ON-state current of 1.68 x 10-5 Amp & OFF-state Current reduced from 7. 83x 10<sup>-11</sup> Amp to 5.13 x 10<sup>-12</sup> Amp and ION / IOFF ratio has increased from 3.22 x 10<sup>5</sup> to 3.27 x 10 compared to conventional dual gate Tunnel field effect transistor. Therefore, this device is suitable for low power applications

doi: 10.5829/ije.2023.36.06c.11

#### **1. INTRODUCTION**

As the Semiconductor industry leads into nanoscale technology and the device dimensions are continuously downscaling, The Hetero Dielectric Tunnel field effect transistor is the alternative because of its tunneling mechanism, lower leakage current and reduced short channel effect. Several attempts have been made to improve the electrical properties and drain current characteristics of Tunnel Field Effect transistors [1]. Due to its band to band tunneling and vide variety of methods and strategies are developed in the Tunnel Field Effect transistors devices The gate-oxide semiconductor materials being low-k dielectric material such as Silicon Dioxide, high-k dielectric materials as Hafnium oxide and gate-electrodes play vital role in the improvement of electrical and drain current characteristics [2]. The source-side oxide regions of Tunnel Field Effect transistors device will improve on-current, and the drainside oxide region reduces the off-current. Therefore, the tunneling mechanism occurs in the source-channel region during the on-state condition and same tunneling process will determine the ambipolar off-current [3].

The Nanoscale Tunnel Field Effect transistors is an advanced transistor suitable for digital circuit applications and Radio Frequency applications based on improved drain current characteristics [4]. In Tunnel Field Effect transistors the tunnel width is narrow, therefore electrons can tunnel from the p+ source to the channel for conduction and higher band to band tunneling generation rate. As a result, the channel has more carriers accessible for current conduction. Due to their lower power dissipation, tunnel field-effect transistors are widely used in nanoscale semiconductor devices and can operate at reduced bias voltages [5].

In the reverse bias structure, Tunnel Field Effect Transistor exhibits a miniaturized short channel effect, reduced leakage current, and decreased temperature dependency and has major issues correlated to lower drain current, and lacking in high-frequency applications. To overcome these issues, several techniques were introduced by the researchers as gate overlap and

<sup>\*</sup>Corresponding Author Email: vahividi@gmail.com (B. Balaji)

Please cite this article as: S. Howldar, B. Balaji, K. Srinivasa Rao, Design and Qualitative Analysis of Hetero Dielectric Tunnel Field Effect Transistor Device, *International Journal of Engineering, Transactions C: Aspects*, Vol. 36, No. 06, (2023), 1129-1135

underlap engineering on the drain side, source extension engineering, drain extension engineering, gate work function engineering, pocket layer, and hetero dielectric materials to increase the on-current (Ion) [6]. To increase the drain current characteristics all the approaches depend on tunneling narrow width and a large electric field (E). In addition, different heterostructures come up for low band gap semiconductor materials Gallium arsenide, and Indium phosphide to achieve improved current. But due to the complexity of these structures hard to achieve a good on-state current. Due to the large band gap and effective mass, all the Tunnel Field Effect transistors devices provide a lower band-to-band tunneling rate. Therefore, heterostructure Tunneling Field Effect Transistor with low band gap material is preferable enhance on-state performance to characteristics [7].

We proposed a hetero dielectric Tunnel Field Effect transistors device made of Nanomaterial oxide with a spacer to combine all the low-k dielectric material such as Silicon Dioxide and high-k dielectric semiconductor materials such as Hafnium Oxide to achieve good tunneling mechanism and reduce leakage. The high-k dielectric material hafnium oxide and Titanium Dioxide are used as spacer material on both sides of dual metal gate to improve device drain current (Id) [8]. The lower bandgap should increase the device drain current characteristics whereas the higher band gap should reduce the ambipolar current in the device. Due to lower operating voltage, the Ion/Ioff ratio decreases. Therefore, we applied spacer material as high-k dielectric material being hafnium oxide on both sides of the dual metal gate and having smaller tunneling bandgap has been introduced in the proposed device [9].

In this paper, we have considered spacer engineering on both sides of a dual gate with a high-k dielectric material as hafnium oxide along with hetero dielectric and hetero junction engineering techniques and Nanomaterial oxide materials to improve Ion current and lower the ambipolar current. Due to the spacer engineering technique, the drain-channel interface could be suppressed because of increased depletion width. In the proposed device hetero dielectric material is used to modulate the tunneling barrier at source-channel and drain channel interfaces. High-k dielectric material Hafnium oxide is chosen for improved results. The drain current characteristics of the device have been carried out and compared with other models such as Conventional -Tunnel Field EffectTransistor, Dual Gate- Tunnel Field Effect, and Hetero junction Dual Gate - Tunnel Field Effect. The simulations have been performed and extracted using the Silvaco Technology Computer Aided Design simulator [10].

The organization of the paper is as follows: The proposed Nanoscale device, its models, methods, and device parameters are presented in second section. The third section presented results and discussion of drain current characteristics such as ion current, Ioff current, and Ion/Ioff ratio. The final section is presented as conclusion.

# **2. STRUCTURE**

Figure 1 shows 2-Dimensional view of conventional Tunnel Field Effect transistor with Hafnium Oxide, Silicon Dioxide , and Nanomaterial oxide materials are utilized for the design. The device dimension (Wd) is 60 nanometers long and gate length (Lg) of 5 nanometers, a source length (Ls) of 27.5 nanometers, a drain length of 27.5 nanometers, and a channel length of 5 nanometers. The symmetric dual metal gate is connected on top and bottom with oxide material with Silicon Dioxide. 5nm channel length is connected equally from source and drain terminals [11].

Figure 2 shows the 2-Dimensional view of Dual Material Gate Tunnel Field Effect transistor where the materials such as Hafnium Oxide, Silicon Dioxide, and Nanomaterial oxide materials are used. An asymmetric dual metal gate is connected on top and bottom with oxide material with Silicon Dioxide. 5nm channel length is connected equally from source and drain terminals [12].

Figure 3 shows the 2-Dimensional view of view of High-k Dielectric material with Hafnium Oxide Spacer. The material utilized for the spacer in this Spacer Tunnel Field Effect Transistor is Hafnium Oxide [11, 12]. Spacers are used at the top and bottom gates of the source side and drain side. The spacers are 7nm long and 2nm wide, with a length of 7nm and a width of 2nm are utilized in Silvaco TCAD tool along with Nanomaterial oxides [13].

Figure 4 depicts the 2-Dimensional view of structure of the Hetero–Dielectric Tunnel Field Effect Transistor

Figure 1. Structure of Conventional device

Figure 2. Structure of Dual Material Gate Tunnel Device

Figure 3. Structure of Spacer Tunnel Device

Figure 4. Proposed device

in this structure interface layer improves contact between the semiconductors [14]. The device dimension (Wd) is 60 nanometers long, with a gate length (Lg) of 5 nanometers, source length (Ls) of 27.5 nanometers, and drain length of 27.5 nanometers. The material utilized for the Spacer is Hafnium Oxide. Spacers are used at both sides of the source and the drain. The spacers are 7nm long and 2nm wide, with a length of 7nm and a width of 2nm [15].

In the above architectures, a lightly doped channel is employed with a  $1 \times 10^{16}$  cm<sup>-3</sup> doping concentration, and an increased doping concentration of  $5 \times 10^{19}$  cm<sup>-3</sup> is employed in the channel to introduce spacer at the end of the source side with the implantation method in the fabrication process for adopting channel engineering.

Table 1 shows the effective parameters used to simulate the Hetero Dielectric- Dual Material Gate Spacer Tunnel Field Effect Transistor device using the Silvaco tool. The on-state current and off-state current of various architectures and variations of channel length are shown in Tables 2, 3 and 4.

In Symmetrical Dual-k Hetero– Dielectric Tunnel Field Effect Transistor, the length ratio of Hafnium oxide and Low-k is varied from 1:14 to 14:1 over the total spacer length of 10nm. The spacer length of Hafnium oxide and Low-k plays a significant role in describing the electrostatics of a gate-S/D underlap in the device. For underlap architecture, high-permittivity (k) spacer material modulates the charge transport dynamics inside the channel and the underlap region.

The technical report of the proposed device is analyzed with a 2D simulation tool SILVACO for striving design. To obtain the optimum structure of the device, enhanced meshing is used to design the device.

| Parameter                                 | Proposed Values               |

|-------------------------------------------|-------------------------------|

| Device Length(W <sub>L</sub> )            | 60nm                          |

| Gate Length(L <sub>G</sub> )              | 10nm                          |

| Source Length(L <sub>S</sub> )            | 25nm                          |

| Drain Length(L <sub>D</sub> )             | 25nm                          |

| Channel Length(L <sub>C</sub> )           | 10nm                          |

| Doping of Source(D <sub>S</sub> )         | $1 x 10^{17} cm^{-3}$         |

| Doping of Drain(D <sub>D</sub> )          | $1 x 10^{18} \text{ cm}^{-3}$ |

| Doping of Channel(D <sub>C</sub> )        | $1 x 10^{20} \text{ cm}^{-3}$ |

| Metal Gate Work Function(W <sub>F</sub> ) | 4.8eV                         |

| Thickness of SiO <sub>2</sub>             | 2nm                           |

| Thickness of HfO <sub>2</sub>             | 3nm                           |

TABLE 1. Used Parameters for the proposed structure

The Two-Dimensional graphical representation of the proposed dielectric material Spacer Tunnel Field Effect Transistor is extensively used for low power digital applications due to its improved performance parameters.

The originality of the proposed structure is designed from one to one i.e conventional Tunnel Field Effect Transistor, dual material gate, symmetrical spacer material and hetero dielectric Tunnel Field Effect Transistor with length of dual gate is 5nm and thickness of each oxide layer 2nm, 3nm using Silvaco tool.

The future prospect of the proposed device could be designed with Low-k source side Asymmetric Spacer Halo doped Tunnel Field Effect Transistor, then there is a 74% reduction in gate capacitance and 31% reduction in intrinsic Delay

The proposed dual material hetero dielectric spacer Tunnel device is invented using Silvaco tool with gate length of 5nm. In this model both high-k and low-k materials are symmetrical. Therefore, the drain current characteristics of proposed model is higher than the existed models.

# **3. RESULTS AND DISCUSSION**

**3. 1. Drain Current** The following equation is used to drain current of any conventional device:

I drain -sat = z b(x) q n(x) v(x)

where z is channel width, b(x) is effective depth of the channel, q is electron charge, n(x) is electron density, and v(x) is electron velocity.

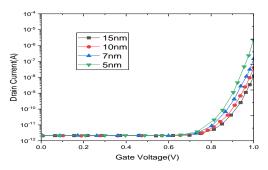

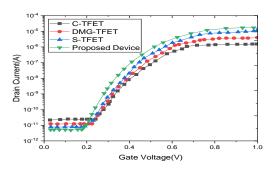

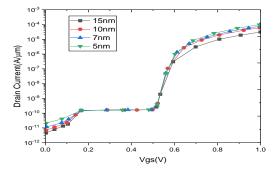

The drain current and gate voltage characteristics of the proposed device Hetero– Dielectric -Dual Material Gate Tunnel Field Effect Transistor for varied Gate lengths of 5nm, 7nm, 10nm, and 15nm are shown in Figure 5. The drain current of the proposed device increased as the length of gate is reduced [16-18]. Figure 6 shows that the proposed device drain current Vs gate voltage, where the drain current of the device is higher than the conventional device and it has high drain current characteristics [19].

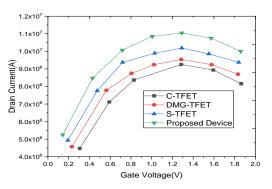

In Figure 7, the Hetero– Dielectric -Dual Material Gate –Tunnel Field Effect Transistor device's  $I_{ON}$  to Ioff ratio rises with increasing high-k dielectric length up to 5 nm. Because of a significant increase in ON-state current, the current ratio has increased exponentially. However, as Ioff and saturated Ion increase above 5 nm, the ratio decreases significantly. As a result, the lengths of Hafnium dioxide and Silicon dioxide dielectric materials are 5 and 10 nanometers, respectively.

Figure 8 depicts the effect of Hafnium dioxide Spacer length variation on the suggested structure's transfer properties. As the Spacer length of Hafnium dioxide is increased, on current (Ion) increases to 5 nm, and then drain current (Id) increases at lengths of 7nm and10 nm. Because the tunneling barrier width at the channel-drain interface is reduced, the ambipolar current steadily increases. We chose 10 nm and 20 nm for the Hafnium dioxide and Silicon dioxide layers, respectively, to retain a greater Ion/Ioff ratio without impairing the Hetero– Dielectric –Dual Material Gate-Tunnel Field Effect Transistor structure's OFF current. The adjusted 5nm gate length is proposed for this structure, because of improved performance characteristics [20].

Figure 5. Drain current versus Gate voltage with different Gate length

Figure 6. Drain current versus Gate voltage for different structures

Figure 7. Variation of on current for different structures

Figure 8. Drain current versus Gate voltage with Spacer material

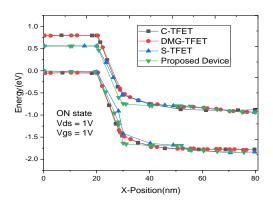

Due to the applied narrow band gap material as silicon dioxide on the source side, the heterojunction Tunnel Field Effect Transistor demonstrates improved band bending is shown in Figure 9. Based on high-k dielectric materials such as Hafnium oxide at the tunneling side, the width of Hetero Dielectric-Dual Material Gate- Tunnel Field Effect Transistor is reduced when compared to other structures [21, 22]. As a result, a large number of carriers can tunnel from the source to the channel region, resulting in a greater on-state current. Because of an increase in depletion width in the drain area, both Dual Material Gate- Tunnel Field Effect Transistor and Spacer-Tunnel filed effect transistor exhibit reduced band bending. On the drain side of the Hetero- Dielectric -Dual Material Gate -Tunnel Field Effect Transistor, Silicon dioxide also reduced.

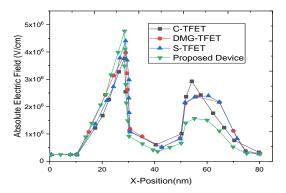

**3. 2. Electric Field** Figure 10 shows the electric field distribution of proposed device with device length in state condition (Vgs = 1.5V) and ambipolar voltage (Vgs = 1.5V) states. Due to the electric field crowding effect, the breakdown should be happening at the gate nearer the drain. Hence the electric field concentration has increased compared to conventional devices. Based proposed structure, the electric field concentration is more compared to the electric field distribution of other

Figure 9. Energy band diagram of the proposed device

Figure 10. Absolute electric field of proposed device

devices [23]. The reduction in the tunneling barrier width in heterojunction Tunnel Field Effect Transistor s results in a greater electric field along the source-channel interfaces, as shown in the figure. The use of Hafnium oxide as a dielectric in the source channel when compared to previous simulated structures, the suggested Hetero– Dielectric –Dual Material Gate –Tunnel Field Effect Transistor has less ambipolar behavior [24, 25].

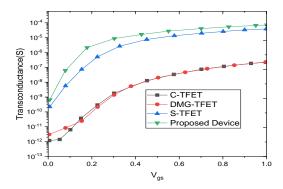

**3.3. Transconductance** The Trans conductance versus Gtae voltage for different structures are shown in Figure 11. The proposed device attains the highest packing density due to better current flow in the device. Hence this structure provides more improvement in transcondutance. To achieve proper gain of device high transconductance is needed and calculated. Using the Silvaco tool transistor characteristics simulations are performed dielectric is used, resulting in less band-to-band tunneling process will exist [26].

The higher drain current driving power of charge carriers, gm increases exponentially with an increase in gate bias. Because of higher drain current (Id), heterojunction Tunnel Field Effect Transistor has a higher gm value than Dual Material Gate-TFET and Spacer-Tunnel Field Effect Transistor. However, due to mobility degradation, it decreases with a bigger magnitude of gate bias. Another essential measure for estimating device efficiency is the transconductance generation factor [27, 28]. Transconductance generation factor demonstrates the efficiency with which current can be converted into transconductance (speed).

$$Transconductance (G_m) = \frac{\partial I_{ds}}{\partial V_{gs}}$$

(1)

The performance Improvements of proposed hetero dielectric structure compared with on current, leakage current and its ratio for three different devices are shown in Table 2. Based on comparison on current is increases, leakage current reduces and its ratio is increases. Therefore, the proposed device performance parameters are improved compared to previous devices (Tables 3 and 4) [29, 30].

Figure 11. Comparison of Transconductance for the proposed device

**TABLE 1.** On current and off current for different Structures

| Architecture    | IOFF     | ION     | ION/IOFF |

|-----------------|----------|---------|----------|

| C-TFET          | 2.17E-11 | 1.51E-6 | 6.95E+4  |

| DMG-TFET        | 1.23E-11 | 3.97E-6 | 3.22E+5  |

| S-TFET          | 7.83E-12 | 1.03E-5 | 1.31E+6  |

| Proposed Device | 5.13E-12 | 1.68E-5 | 3.27E+6  |

**TABLE 2.** Comparison of on current and off current for the hetero structure

| netero su ucture |          |         |          |  |  |

|------------------|----------|---------|----------|--|--|

| Architecture     | IOFF     | ION     | ION/IOFF |  |  |

| C-TFET           | 1.00E-9  | 7.44E-8 | 7.44E+1  |  |  |

| DMG-TFET         | 6.25E-11 | 7.65E-8 | 1.22E+3  |  |  |

| S-TFET           | 1.23E-11 | 1.90E-5 | 1.54E+6  |  |  |

| Proposed Device  | 7.03E-12 | 3.52E-5 | 5.00E+6  |  |  |

| Gate Length | IOFF     | ION     | ION/IOFF |

|-------------|----------|---------|----------|

| 15nm        | 2.05E-12 | 1.23E-8 | 6.00E+3  |

| 10nm        | 2.05E-12 | 4.02E-8 | 1.96E+4  |

| 7nm         | 2.15E-12 | 1.49E-7 | 6.93E+4  |

| 5nm         | 2.15E-12 | 2.27E-6 | 1.03E+6  |

**TABLE 4.** On current and off current for the proposed device with the variation of Gate Length

# 4. CONCLUSION

In this paper, we have designed and analyzed the DC performance analysis of Hetero- Dielectric Tunnel Field Effect Transistor (Hetero Dielectric -Nanowire-Tunnel Field Effect Transistor) with spacer using Silvaco tool in sub 5nm node. The high-k dielectric material hafnium oxide as spacer material is placed on both sides of the dual metal gates. The impact of the proposed device is to reduce the ambipolar current and significantly increase the drain current compared to dual gate Tunnel Field Effect Transistor. The proposed structure with potential high-k dielectric material being hafnium oxide, as a spacer on both sides of the gate has improved better performance over conventional Dual gate Tunnel Field Effect Transistor. Due to maximum drain currents (Id), less sub-threshold swing (SS), lower leakage current (Ioff), greater trans conductance (gm), and larger drain conductance (O) the proposed Hetero Dielectric-Nanowire -Tunnel Field Effect Transistor is useful in low power applications

#### **5. REFERENCES**

- Cui, N., Liu, L., Xie, Q., Tan, Z., Liang, R., Wang, J. and Xu, J., "A two-dimensional analytical model for tunnel field effect transistor and its applications", *Japanese Journal of Applied Physics*, Vol. 52, No. 4R, (2013), 044303. doi: 10.7567/JJAP.52.044303.

- Bardon, M.G., Neves, H.P., Puers, R. and Van Hoof, C., "Pseudotwo-dimensional model for double-gate tunnel fets considering the junctions depletion regions", *IEEE Transactions on Electron Devices*, Vol. 57, No. 4, (2010), 827-834. doi: 10.1109/TED.2010.2040661.

- Gholizadeh, M. and Hosseini, S.E., "A 2-d analytical model for double-gate tunnel fets", *IEEE Transactions on Electron Devices*, Vol. 61, No. 5, (2014), 1494-1500. doi: 10.1109/TED.2014.2313037.

- Yadav, M., Bulusu, A. and Dasgupta, S., "Two dimensional analytical modeling for asymmetric 3t and 4t double gate tunnel fet in sub-threshold region: Potential and electric field", *Microelectronics Journal*, Vol. 44, No. 12, (2013), 1251-1259. doi: 10.1007/s12633-021-01509-2.

- Liao, X., Tsui, K., Liu, H., Chen, K. and Sin, J., "A step-gateoxide soi mosfet for rf power amplifiers in short-and mediumrange wireless applications", in 2003 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2003. Digest of Papers., IEEE., (2003), 33-36.

- Boucart, K. and Ionescu, A.M., "Double-gate tunnel fet with high-\$\kappa \$ gate dielectric", *IEEE Transactions on Electron Devices*, Vol. 54, No. 7, (2007), 1725-1733. doi: 10.1109/TED.2007.899389.

- Luong, G.V., Narimani, K., Tiedemann, A., Bernardy, P., Trellenkamp, S., Zhao, Q. and Mantl, S., "Complementary strained si gaa nanowire tfet inverter with suppressed ambipolarity", *IEEE Electron Device Letters*, Vol. 37, No. 8, (2016), 950-953. doi: 10.1109/LED.2016.2582041.

- Hu, V.P.-H., Chiu, P.-C. and Lu, Y.-C., "Impact of work function variation, line-edge roughness, and ferroelectric properties variation on negative capacitance fets", *IEEE Journal of the Electron Devices Society*, Vol. 7, (2019), 295-302. doi: 10.1109/JEDS.2019.2897286.

- Asthana, P.K., Ghosh, B., Goswami, Y. and Tripathi, B.M.M., "High-speed and low-power ultradeep-submicrometer iii-v heterojunctionless tunnel field-effect transistor", *IEEE Transactions on Electron Devices*, Vol. 61, No. 2, (2014), 479-486. doi: 10.1039/C4RA00538D.

- Balaji, B., Srinivasa Rao, K., Girija Sravani, K., Bindu Madhav, N., Chandrahas, K. and Jaswanth, B., "Improved drain current characteristics of HFO<sub>2</sub>/SiO<sub>2</sub> dual material dual gate extension on drain side-tfet", *Silicon*, (2022), 1-6. doi: 10.1007/s12633-022-01955-6.

- Wadhwa, G. and Raj, B., "Design, simulation and performance analysis of jltfet biosensor for high sensitivity", *IEEE Transactions on Nanotechnology*, Vol. 18, (2019), 567-574. doi: 10.1109/TNANO.2019.2918192.

- Kumar, P.K., Balaji, B. and Rao, K.S., "Performance analysis of sub 10 nm regime source halo symmetric and asymmetric nanowire mosfet with underlap engineering", *Silicon*, Vol. 14, No. 16, (2022), 10423-10436. doi: 10.1007/s12633-022-01747-y.

- Balaji, B., Rao, K.S., Sravani, K.G. and Aditya, M., "Design, performance analysis of gaas/6h-sic/algan metal semiconductor fet in submicron technology", *Silicon*, (2022), 1-5. doi: doi: 10.1007/s12633-021-01545-y.

- Narang, R., Reddy, K.S., Saxena, M., Gupta, R. and Gupta, M., "A dielectric-modulated tunnel-fet-based biosensor for label-free detection: Analytical modeling study and sensitivity analysis", *IEEE Transactions on Electron Devices*, Vol. 59, No. 10, (2012), 2809-2817. doi: 10.1109/LED.2011.2174024.

- Kumar, N. and Raman, A., "Design and investigation of chargeplasma-based work function engineered dual-metalheterogeneous gate si-si 0.55 ge 0.45 gaa-cylindrical nwtfet for ambipolar analysis", *IEEE Transactions on Electron Devices*, Vol. 66, No. 3, (2019), 1468-1474. doi: 10.1109/TED.2019.2893224.

- Morifuji, E., Yoshida, T., Kanda, M., Matsuda, S., Yamada, S. and Matsuoka, F., "Supply and threshold-voltage trends for scaled logic and sram mosfets", *IEEE Transactions on Electron Devices*, Vol. 53, No. 6, (2006), 1427-1432. doi: 10.1109/TED.2006.874752.

- Musalgaonkar, G., Sahay, S., Saxena, R.S. and Kumar, M.J., "Nanotube tunneling fet with a core source for ultrasteep subthreshold swing: A simulation study", *IEEE Transactions on Electron Devices*, Vol. 66, No. 10, (2019), 4425-4432. doi: 10.1109/TED.2019.2933756.

- Guin, S., Chattopadhyay, A., Karmakar, A. and Mallik, A., "Impact of a pocket doping on the device performance of a schottky tunneling field-effect transistor", *IEEE Transactions on Electron Devices*, Vol. 61, No. 7, (2014), 2515-2522. doi: 10.1109/TED.2014.2325068.

- Lee, J.W. and Choi, W.Y., "Design guidelines for gate-normal hetero-gate-dielectric (GHG) tunnel field-effect transistors (tfets)", *IEEE Access*, Vol. 8, (2020), 67617-67624. doi: 10.1109/ACCESS.2020.2985125.

- Naraiah, R., Balaji, B., Radhamma, E. and Udutha, R., "Delay approximation model for prime speed interconnects in current mode", *IJITEE*, *ISSN*, (2019), 2278-3075. doi: 10.35940/ijitee.I8019.078919.

- Singh, N., Buddharaju, K.D., Manhas, S.K., Agarwal, A., Rustagi, S.C., Lo, G., Balasubramanian, N. and Kwong, D.-L., "Si, sige nanowire devices by top-down technology and their applications", *IEEE Transactions on Electron Devices*, Vol. 55, No. 11, (2008), 3107-3118. doi: 10.1109/TED.2008.2005154.

- Han, K., Zhang, Y. and Deng, Z., "A simulation study of gate-allaround nanowire transistor with a core-substrate", *IEEE Access*, Vol. 8, (2020), 62181-62190. doi: 10.1109/ACCESS.2020.2983724.

- Zou, B., Sun, H., Guo, H., Dai, B. and Zhu, J., "Thermal characteristics of gan-on-diamond hemts: Impact of anisotropic and inhomogeneous thermal conductivity of polycrystalline diamond", *Diamond and Related Materials*, Vol. 95, (2019), 28-35. doi: 10.1088/1361-6641/ac1c4f.

- Dipalo, M., Gao, Z., Scharpf, J., Pietzka, C., Alomari, M., Medjdoub, F., Carlin, J.-F., Grandjean, N., Delage, S. and Kohn, E., "Combining diamond electrodes with gan heterostructures for harsh environment isfets", *Diamond and Related Materials*, Vol. 18, No. 5-8, (2009), 884-889. doi: 10.1016/j.diamond.2009.01.011.

- Sachid, A.B., Manoj, C., Sharma, D.K. and Rao, V.R., "Gate fringe-induced barrier lowering in underlap finfet structures and its optimization", *IEEE Electron Device Letters*, Vol. 29, No. 1, (2007), 128-130. doi: 10.1109/LED.2007.911974.

- Sahay, S. and Kumar, M.J., "A novel gate-stack-engineered nanowire fet for scaling to the sub-10-nm regime", *IEEE Transactions on Electron Devices*, Vol. 63, No. 12, (2016), 5055-5059. doi: 10.1109/TED.2016.2617383.

- Sachid, A.B., Chen, M.-C. and Hu, C., "Finfet with high-\$\kappa \$ spacers for improved drive current", *IEEE Electron Device Letters*, Vol. 37, No. 7, (2016), 835-838. doi: 10.1109/LED.2016.2572664.

- Francis, D., Faili, F., Babić, D., Ejeckam, F., Nurmikko, A. and Maris, H., "Formation and characterization of 4-inch gan-ondiamond substrates", *Diamond and Related Materials*, Vol. 19, No. 2-3, (2010), 229-233. doi: 10.1016/j.diamond.2009.08.017.

- Pal, P.K., Kaushik, B.K. and Dasgupta, S., "Investigation of symmetric dual-k spacer trigate finfets from delay perspective", *IEEE Transactions on Electron Devices*, Vol. 61, No. 11, (2014), 3579-3585. doi: 10.1109/TED.2014.2351616.

- Sachid, A.B., Lin, H.-Y. and Hu, C., "Nanowire fet with corner spacer for high-performance, energy-efficient applications", *IEEE Transactions on Electron Devices*, Vol. 64, No. 12, (2017), 5181-5187. doi: 10.1109/TED.2017.2764511.

## Persian Abstract

# چکیدہ

در این مقاله یک ترانزیستور اثر تونل دی تریک هترو با اسپیزر در دو طرف دروازه پیشنهاد شده و ویژگی های عملکرد آن را با استفاده از طراحی به کمک کامپیوتر فناوری اطلس در رژیم 5nm مورد تجزیه و تحلیل قرار داده است .جریان نشت تونل زنی باند به باند با معرفی مواد هتروجکشن و اسپیزر دی هترو دی تریک در ساختار پیشنهادی کاهش خواهد یافت .در ترانزیستور اثر میدان تونل دی هترو دی تریک، دروازه فلزی مضاعف و اسپیزر دی لوکتریک با k بالا بر روی نوسان جریان و زیرمدارندگی بهبود می یابد .اسپیزر اکسید دی تریک بالا K هافنیوم (IV) در دو طرف منبع قرار می گیرد و تخلیه می شود تا مکانیسم تونل زنی وارد شود .دستگاه پیشنهادی در گره 5nm ویژگی های DC مانند جریان حالت (IV) به مافنیوم (IV) در دو طرف منبع قرار می گیرد و تخلیه می شود تا مکانیسم تونل زنی وارد شود .دستگاه پیشنهادی در گره 5nm ویژگی های DD مانند جریان حالت ON بالا ION بالا ION مافنیوم (IO) در از 7 کاهش داده است IO<sup>11</sup> میر به 20 x 10<sup>11</sup> میر و ION ماند الاکت IOFF از تریک بالا IOF نوان دسبت به ترانزیستور میدان تونل دروازه دوگانه معمولی افزایش یافته است .بنابراین این دستگاه برای کاربردهای کم توان مانیک IDFF از IOFF از ION بالا ION در دو میدان تونل دروازه دوگانه معمولی افزایش یافته است .بنابراین این دستگاه برای کاربرده کر توان مانسب