# International Journal of Engineering

Journal Homepage: www.ije.ir

# Performance Analysis and Optimization of Asymmetric Front and Back Pi Gates with Dual Material in Gallium Nitride High Electron Mobility Transistor for Nano Electronics Application

### Y. Gowthami, B. Balaji\*, K. Srinivasa Rao

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Green Fields, Vaddeswaram, Guntur, Andhra Pradesh, India

#### PAPER INFO

ABSTRACT

Paper history: Received 12 December 2022 Received in revised form 20 March 2023 Accepted 28 March 2023

Keywords: Dual Floating Material Drain Current Leakage Current Ron Technology Computer Aided Design The impact of aluminium nitride (AlN) Spacer, Gallium Nitride (GaN) Cap Layer, Front Pi Gate (FG) and Back Pi Gate(BG), Dual Floating material High K dielectric material such as Hafnium dioxide (HfO<sub>2</sub>), Aluminium Oxide (Al<sub>2</sub>O<sub>3</sub>), Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) on Aluminium Galium Nitride/ Gallium Nitride (AlGaN/GaN), Heterojunction High Electron Mobility Transistor (HEMT) of 6nm technology is simulated and extracted the results using the Silvaco Atlas Technology Computer-Aided Design (TCAD) tool. The importance of High K dielectric materials like Al2O3 and Si3N4 were studied for the proposal of GaN HEMT. AlN, GaN Cap Layers, and High K Dielectric material are layered one on another to overcome the conventional transistor draw backs like surface defects, scattering of the electron, and less mobility of electron. Hot electron effect is overcome by Pi type gate. Triple tooth floating material is placed in the buffer layer to improve breakdown voltage. Therefore, by optimizing the HEMT structure the inabilities for certain devices are converted to abilities. The dependency on DC characteristics and RF characteristics due to GaN Cap Layers, Multi gate (FG &BG), and High K Dielectric material, Dual triple tooth material in buffer layer with recessd gate is established. Further Compared Single Gate (SG) Passivated HEMT, Double Gate (DG) Passivated HEMT, Double Gate Triple (DGT) Tooth Passivated HEMT, High K Dielectric Front Pi Gate (FG) and Back Pi Gate (BG), Asymmetric High K Dielectric Front Pi Gate (FG) and Back Pi Gate (BG) with recessed gate Nanowire HEMT. It was observed that the proposed resulted with increased Drain Current (Ion) of 7.5 (A/mm), low Leakage current (Ioff) 3E-15 (A), Transconductance (Gm) of 4.8 (S/mm), Drain Conductance (G<sub>d</sub>) of 2.5 (S/mm), Maximum Oscillation frequency (Fmax) 745 GHz, Minimum Threshold Voltage (Vth) of -4.5V, On Resistance (Ron) of 0.12(Ohms) at V<sub>gs</sub>=0V.

doi: 10.5829/ije.2023.36.07a.08

## **1. INTRODUCTION**

As Gallium Nitride (GaN) wide band gap material, it possesses exclusive required material properties like high thermal stability, high breakdown voltage, high saturation velocity voltage, high current density, and high saturation velocity it can be implemented in high-power microwave applications [1]. In semiconductor optoelectronics models, GaN-based transistors have its own importance. Heterostructure, high electronic mobility Transistor is formed between semiconductor material of different Band gaps where electrons are generated and travel with rapid speed (mobility of electron) [2]. The large bandgap, high velocity, high current, and less On Resistance (Ron) characteristics, reflect high efficiency for HEMT [3]. The size reduction is the current trend in implementation to result in high performance but the reduction in size of transistor, device is permissible to some extent only if the device is further decreased which leads to short channel effects, leakage current [4]. A small transistor means more numbers in the transistor in the same area with a wafer of the same size,

Please cite this article as: Y. Gowthami, B. Balaji, K. Srinivasa Rao, Performance Analysis and Optimization of Asymmetric Front and Back Pi Gates with Dual Material in Gallium Nitride High Electron Mobility Transistor for Nano Electronics Application, *International Journal of Engineering, Transactions A: Basics*, Vol. 36, No. 07, (2023), 1269-1277

<sup>\*</sup>Corresponding Author Institutional Email: <u>vahividi@gmail.com</u> (B. Balaji)

more chips per wafer the manufacturer can fabricate. It indicates the advancement of technology towards nano world [5]. High performance is obtained due to advanced nanowire technology [6]. For example, it reflects in clock time per instruction within the same time more instruction can be executed [7]. More function units in one chip can be integrated reducing the power consumption requirements [8]. Reduction in transistor size focuses on decreasing gate length [9]. When clock speed is taken into consideration for processors, the gate length is the primary to be considered. More we reduce the gate length faster than the device works; very fast calculation is performed [10-12]. High doping causes drain-induced barrier lowering (DIBL) which causes the current to leak, high subthreshold conduction is the state where FET, which is not completely ON, not completely OFF [13]. This will be presented if the transistor gate length is reduced beyond the limitation. To overcome this limitation Heterojunction High Electron Mobility Transistor came (HEMT) into existence [14, 15]. Gallium Arsenide (GaAs), Gallium Nitride (GaN), Indium Phosphide (InP), and Silicon Carbide (SiC) can meet the requirements. Among these materials, in highpower applications GaN make its use due to its high saturation velocity, high wideband gap, and high critical field properties [16, 17]. The material properties and electronic properties of GaAs, GaN, SiC, and Si are sorted in Table 5. From this table content, it is observed that Gallium Nitride ideal candidate to proceed for implementation in the advancement of Power Electronics [18]. It is observed by Johnson's figure of merit that GaN ideal candidate for high temperature and high power due to its high electron mobility, saturation velocity, and high breakdown voltage [19]. The narrow channel plays a key role that triggers the device to work at microwave frequencies, this is provided by GaN [20]. HEMT is constructed by deploying two semiconductor substances with identical lattice constant, and distant band gap materials are stacked on one another. At the interjunction of these two material Bidirectional Electron Gas (2DEG) is formed. A broad class of HEMTs is existent namely Gama gate, T gate, Gate Field plate (GFP), Camel shape Gate (CG), Discrete Field Plate (DFP), Multiple Grating Field Plate (MGFP) Gate HEMT [21]. These are limited by Early High Leakage current, Breakdown effects, and shorter channel effects. Conventional transistors are optimized to overcome these effects [22]. For the existing HEMT to improve the characteristics of the device GaN layers, Front Pi Gate, and Back Pi Gate are incorporated [23]. These Cap layers passivation layers provide sealing the first layer of nanowire HEMT structure from external atmospheric fluctuations. The proposed Asymmetric High K Dielectric Front Pi Gate (FG) and Back Pi Gate (BG) with recessed gate Nanowire HEMT overcomes the limitation of Dual gate HEMT and exhibits optimized

nanowire HEMT Structure which gives optimistic DC and RF characteristics [24]. The results show that high K dielectric FG & BG nanowire HEMT results improved on current, trans conductance, drain conductance, maximum oscillation frequency, improved cutoff frequency, with reduced leakage current.

### **2. STRUCTURE**

The complete structure for the proposed Asymmetric Front Pi Gate &Back Pi Gate recessed with Dual floating material in buffer layer high electron mobility transistor (HEMT) device with the gate electrode, Source & Drain is shown in Figure 1. The High K Dielectric materials HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, TiO<sub>2</sub>, Si, and Si<sub>3</sub>N<sub>4</sub> with K values and gap (EV) are listed in Table 1.

Hafnium oxide (HfO<sub>2</sub>), Silicon (Si). Silicon Dioxide (SiO<sub>2</sub>) Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>), Titanium Dioxide (TiO<sub>2</sub>), and Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>) are the material with High K dielectric constant. These materials play a key role during the process of semiconductor manufacturing [25, 26].

**Figure 1.** High K Dielectric FG-BG G13 & G23 recessed, Dual floating material GaN HEMT nanowire HEMT structure with Si<sub>3</sub>N<sub>4</sub> /Al<sub>2</sub>O<sub>3</sub> passivation layers

**TABLE 1.** High K Dielectric material HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, TiO<sub>2</sub>, Si, Si<sub>3</sub>N<sub>4</sub> with K Values and gap (EV) are listed in table

| Material                       | K Values | Gap(eV) |  |  |

|--------------------------------|----------|---------|--|--|

| Si                             | 3.9      | 1.1     |  |  |

| SiO <sub>2</sub>               | 3.9      | 9       |  |  |

| $Si_3N_4$                      | 7        | 5.3     |  |  |

| Al <sub>2</sub> O <sub>3</sub> | 9        | 8.8     |  |  |

| TiO <sub>2</sub>               | 80       | 3.5     |  |  |

| HfO <sub>2</sub>               | 25       | 5.8     |  |  |

Among these materials  $SiO_2$  is conventional material where it has been used for past decades in FET, As the size of FET decreases the thickness of  $SiO_2$  is reduced, where the gate capacitance is reduced, and thereby current improved, increasing the device performance.

As the thickness is continuously reduced beyond the limit leakage current increased and led to high power utility (consumptions) and the reliability of the device reduced (degrades). High dielectric materials lead to an increase in gate capacitance, with no leakage effects. The capacitance is related as in the following equation

$$C = \frac{kA\varepsilon_o}{t} \tag{1}$$

A is the area of the capacitance,  $\varepsilon_0$  is free space permittivity, k is dielectric constant of the material, t is capacitor oxide insulator thickness. As the capacitance is related to k by altering k we can improve the capacitance, where the derive current can be improved.

$$I_{D,Sat} = \frac{WC\mu(V_G - V_{th})^2}{2L}$$

(2)

The drain current equation is expressed in Equation (2). Here I<sub>D,Sat</sub> Saturation Drain Current is directly proportional to capacitance, W is the width of the transistor channel, the length of the channel,  $\mu$  is the mobility of the carrier. Vth is the threshold voltage. Since  $Si_3N_4$ ,  $Al_2O_3$  are the elements that are stable thermos dynamically and have a high melting point. Al<sub>2</sub>O<sub>3</sub> has low defect density, highly uniform, scalable in nanometers, is robust nature and can be manufactured. 20nm Al<sub>2</sub>O<sub>3</sub> thickness was deployed. Al<sub>0.75</sub> Ga<sub>0.25</sub>N, Al<sub>0.52</sub>Ga<sub>0.45</sub>N, AlN (Spacer layer), GaN, AlN. Al<sub>0.52</sub>Ga<sub>0.45</sub>N, Al<sub>0.75</sub>Ga<sub>0.25</sub>N these materials are deployed in this sequence respective with 36nm, 38nm, 34nm, 43nm, 34nm, 38nm, 36nm. Spacer Layer is to improve the density of 2DEG (2-Dimensional Electron Gas) Aluminum Nitride is stable at temperatures over 2000° in inert atmosphere. It possesses high thermal conductivity. The unique properties of AlN make its usage in lighting, renewable energy, electronics, optics, etc. It is a solid nitride of Aluminum material. At room temperature, it has approx. 6eV of the band gap. AlN layer used for carrier confinement reduction in alloy scattering improved scattering. GaN Cap layer of 2nm is deployed on the top of the structure. By using GaN cap layer carrier mobility improved, improve transport mechanism. The probability of penetrating the mobility electron into AlGaN is reduced due these layers. High conduction is possible due to the presence of cap layer. Scattering of Alloy reduced, and better confinement of carrier, improved conductivity and mobility is observed by employing the cap layer on the top of heterostructure which proposed makes easy to fabric ohmic contact.

AlGaN is the barrier layer where it is layered with various thicknesses. Leakage current is reduced  $I_{on}/I_{off}$  is increased by this employing. It shows influence in  $R_{on}$

characteristics. High thickness of AlGaN shows the degradation of system performance. It avoids the penetration of electrons into buffer layer. Trapping effects reduction happens so that the dynamic Ron improved [27]. Back barrier layer (BBL) thickness results in reduction in leakage current and dynamic Ron; BBL can be varied from 0 to 200nm; GaN channel is wurtzite crystal structure. It possesses high bandgap of 3.49 (EV) with electron mobility of 900 (cm<sub>2</sub> /vs), electron peak velocity is 2.7 x 107 (cm/s), 2DEG sheet electron density is 20 x 10<sup>12</sup> (cm<sup>-2</sup>), Critical breakdown field 3.3 (MV/cm), thermal conductivity > 1.7 (W/cm-K), Relative dielectric constant  $(\varepsilon_r)$  -9.0 GaN material possess high thermal conductivity, high saturation drift velocity. These properties are required for the device to work in high frequency for having high power switching and to work at high temperatures [28]. Hetero-junction is formed when two material of different band gaps with almost the same lattice constant. The field effect transistor that incorporates hetero-junction is called the high electron mobility transistor (HEMT) [29]. The junction is the interface between two materials. In junction 2-dimensional electron gas raises and flows from the source to drain [30]. The mobility of the electron depends on the material used to form a hetero-junction. Two-dimensional gas characterizes the properties of electron mobility, electron density, gate bias ON current or drive current, Transconductance (gm), threshold voltage (V<sub>th</sub>), and cut-off frequency are determined depending on 2-dimensional electron gas. The improvement of the device's 2D Gas properties play a vital role and understanding the key mechanism of 2DEG is necessary [31]. For high power, high-frequency application AlGaN/GaN Aluminum Galium Nitride/Galium Nitride is used due to its high frequency and high-power application [32]. ∏ shaped gate formed by dividing T gate pillar into 2 symmetric halfs [33]. G13, G14 are the front gate legs and G23, G24 is right gate legs. Experimentation is performed by recessing legs of front gate and back gate with different cases. G13 leg recessed, G13 & G23 recessed, G24 & G14 recessed. Compared to T shaped gate  $\prod$  shaped gate possess low channel temperature. When G13 and G23 is recessed  $\prod$ shaped gate structure thermalization to electron happens and in  $\prod$  gate energy loses so this tends to reduce peak channel temperature [34]. In ∏ structure parasitic capacitance increase which reflects on f<sub>T</sub> reduction; this can be overcome by increasing the height of pillar Gate recess technique improves the device performed by 25 percent [35]. Triple tooth floating metal removes the gate which is virtually present between gate and drain.

The advantages of the proposed structure are to reduce hot electron effect, under which maintaining the device performance stable and well into the millimeter wave frequency range. Proposed dual gate HEMT offers improved transconductance and better immunity and reduces short channel effects subthreshold swing compared to single gate HEMT and disadvantage is the devise should be operated in orderly manner following set of rules to sustain the device performance for longer period

### **3. RESULTS AND DISCUSSION**

Using the Silvaco TCAD tool proposed transistor characteristics simulations are performed. Figure 1 shows high K dielectric FG-BG G13 & G23 recessed, dual floating material GaN HEMT nanowire HEMT structure with  $Si_3N_4$  /Al<sub>2</sub>O<sub>3</sub> passivation layers.The two gates play a key role in improving drain current and conductance of the Device.

Table 2 shows the dimensions of the proposed structure and Table 3 shows the physical properties of dielectric passivation materials  $Si_3N_4$ ,  $SiO_2$ , and  $Al_2O_3$ . Multi combination of  $Al_2O_3$  and  $Si_3N_4$  showed improved results for the proposed structure

Further, the performance of the device can be optimized. GaN cap layers are placed on AlGaN layer to optimize the results. The location of the gate is an important parameter that improves the performance. It

**TABLE 2.** Dimension along the X-axis and Y-axis of the proposed structure

| Material                                | X <sub>min</sub> | X <sub>max</sub><br>(nanometer) | Y <sub>min</sub><br>(nanometer) | Y <sub>max</sub><br>(nanometer) |  |

|-----------------------------------------|------------------|---------------------------------|---------------------------------|---------------------------------|--|

| Al <sub>0.52</sub> Ga <sub>0.45</sub> N | 0                | 320                             | 0                               | 33                              |  |

| AlN                                     | 0                | 320                             | 33                              | 34                              |  |

| Al <sub>0.75</sub> Ga <sub>0.25</sub> N | 0                | 320                             | 34                              | 36                              |  |

| Al <sub>0.52</sub> Ga <sub>0.45</sub> N | 0                | 320                             | 36                              | 38                              |  |

| GaN                                     | 0                | 320                             | 38                              | 43                              |  |

| Al <sub>0.52</sub> Ga <sub>0.45</sub> N | 0                | 320                             | 43                              | 49                              |  |

| AlN                                     | 0                | 320                             | 49                              | 50                              |  |

| GaN                                     | 0                | 320                             | 50                              | 350                             |  |

| Sapphire                                | 0                | 320                             | 350                             | 750                             |  |

**TABLE 3.** Physical properties of dielectric passivation materials

|                                | SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | Si <sub>3</sub> N <sub>4</sub> |

|--------------------------------|------------------|--------------------------------|--------------------------------|

| Thermal Conductivity (w/cm/ k) | 0.014            | 18                             | 0.37                           |

| Melting Point (°C)             | 1600             | 2072                           | 1900                           |

| Density(g/cm <sup>3</sup> )    | 2.2              | 3.95                           | 3.1                            |

| Energy gap at 300k(Ev)         | 9                | 7.6                            | 5                              |

| Refractive index               | 1.46             | 1.77                           | 2.05                           |

| Dielectric Constant            | 3.9              | 10                             | 7.5                            |

consists of a front gate in the upper part and a back gate in the lower part of the proposed structure. The cap layers are placed using GaN material on either side of the front gate and back gate. The top layer gets protection from the external environment, and electron scattering reduces and optimizes performance.

The novel 6nm nanowire HEMT transistor is executed on the Silvaco TCAD tool, and the complete results are discussed in this section.

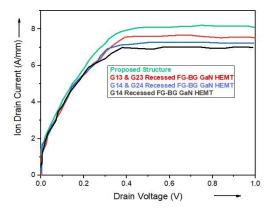

Figure 2 shows drain current changes concerning various drain voltage characteristics of HEMTs with various physical structures of 6 nanometers at Vgs = 0V for the proposed structure that is G13 & G23 recessed with dual floating material, G13 & G23 recessed FG (Front Gate)- BG (Back Gate) GaN HEMT, G14 & G24 recessed FG-BG GaN HEMT, G14 recessed FG-BG GaN HEMT, the proposed structure exhibits high drain current. It results in an increased drain Current (I<sub>d</sub>) of 7.5 A/mm appearing for the proposed structure.

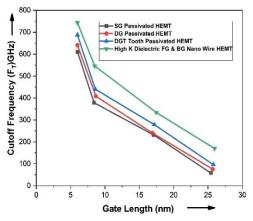

From Equation (3) Cutoff frequency ( $f_T$ ) depends on the length of the gate (Lg) and the saturation velocity of the material and transconductance. As drain current increases, transconductance increases. As the transconductance is directly proportional to the cutoff frequency, the cutoff frequency increased to 743GHz. So, by proper placement of the transistor gate, the required cutoff frequency can be attained.

$$Cutoff \ Frequency = \frac{v_{sat}}{2L_G \Pi} \tag{3}$$

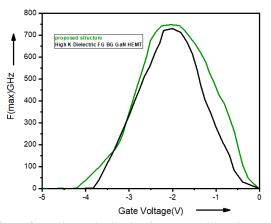

Figure 3 shows the Oscillating frequency ( $f_{max}$ ) concerning gate voltage, of HEMTs with various physical structures of 6 nanometers at Vgs = 0V i.e. For the proposed structure that is G13 & G23 recessed with dual floating material, at gate voltage Vds = 0.2V is shown. It resulted in maximum oscillating frequency ( $f_{Max}$ ) of 743GHz appeared same as High K dielectric FG & BG nanowire HEMT for the proposed structure also.

**Figure 2.** Drain Current changes concerning various Drain voltage characteristics for HEMTs with various physical structures of 6-nanometer technology at Vgs = 0V

**Figure 3.** Maximum Oscillation frequency with various gate voltages for the proposed structure that is G13 & G23 recessed with dual floating material, high K dielectric FG & BG HEMT

Transconductance (gm) is defined as the ratio of change in drain current ( $I_d$ ) to the change in the change in the gate to source voltage ( $V_{GS}$ ) represented in Equation (4):

$$Transconductance = \frac{dI_D}{dV_{GS}} \tag{4}$$

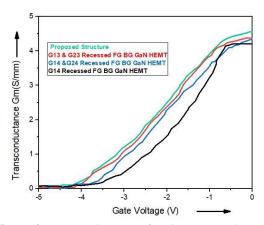

Figure 4 shows Transconductance ( $G_m$ ) concerning gate Voltage V<sub>gs</sub> for HEMTs with various physical structures of 6 nanometers at V<sub>ds</sub> = 0.2V i.e. The proposed structure, G13 & G23 recessed with dual floating material, G13 & G23 recessed FG (Front Gate)-BG (Back Gate) GaN HEMT, G14 & G24 recessed FG-BG GaN HEMT, G14 recessed FG-BG GaN HEMT. It is shown that increased Transconductance of 4.8 (S/mm). Appeared for the proposed structure.

**Figure 4.** Transconductance of various gate voltages for Proposed Structure ,G13 & G23 recessed FG(Front Gate)-BG(Back Gate ) GaN HEMT ,G14 & G24 Recessed FG-BG GaN HEMT ,G14 Recessed FG-BG GaN HEMT at Vds =0.2

As ionized impurities scattering suppressed high mobility for the free carrier is observed and even gate to source resistance also reduced high transconductance is observed due to the usage of higher conduction band discontinuity-based materials. As sufficient space laver distance in gate to channel distance used current in active region is more which makes best use of the proposed structure in precision sensors, advanced radars, power electronics. high gain, high switch speeds, low noise and very good high frequency performance, low parasitic and source resistance are the required drain characteristics for the device to operate in millimeter range frequency. In order to obtain these requirements buffer layers, floating material, recessed gate are included in novel proposed structure.

Figure 5 shows the maximum oscillation frequency with various gate voltages for the proposed structure that is G13 & G23 recessed with dual floating material, high K dielectric FG & BG nanowire HEMT at gate voltage Vds = 0.2V is shown. It resulted same maximum oscillating frequency ( $f_T$ ) of 743GHz, similar to high K dielectric FG & BG GaN HEMT.

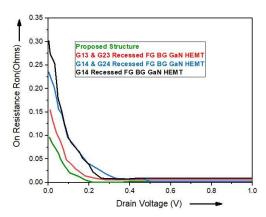

Figure 6 shows On Resistance ( $R_{on}$ ) concerning drain voltage ( $V_{ds}$ ) characteristics of HEMTs with various physical structure 6 nanometers at gate Voltage = 0V i.e., for the proposed structure, G13 & G23 recessed FG (Front Gate)- BG (Back Gate ) GaN HEMT, G14 & G24 recessed FG-BG GaN HEMT, G14 recessed FG-BG GaN HEMT at gate voltage Vgs = 0V is shown. It resulted in on resistance of ( $R_{on}$ ) of 0.12 (Ohms) appeared for the proposed structure.

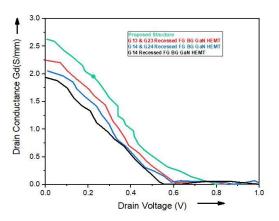

Figure 7 shows drain conductance (G<sub>d</sub>) concerning drain voltage (V<sub>ds</sub>) characteristics of HEMTs with various physical structures of 6 nanometers at V<sub>ds</sub> = 0.2V i.e., for the proposed structure, G13 & G23 recessed FG (Front Gate)- BG (Back Gate) GaN HEMT, G14 & G24 recessed FG-BG GaN HEMT, G14 recessed FG-BG GaN HEMT, V<sub>gs</sub> = 0V is shown.

**Figure 5.** Cut-off frequency variations at different gate lengths for various Physical structures at Vds = 0.2V

**Figure 6.** On Resistance variation to various Drain voltage for Proposed Structure, G13 & G23 recessed FG (Front Gate)- BG(Back Gate ) GaN HEMT ,G14 & G24 Recessed FG-BG GaN HEMT ,G14 Recessed FG-BG GaN HEMT

Figure 7. Drain conductance  $(G_d)$  with respect to drain voltage  $(V_{ds})$  characteristics of HEMTs with various physical structures of 6 nanometers i.e., for Proposed Structure ,G13 & G23 recessed FG(Front Gate)- BG(Back Gate ) GaN HEMT ,G14 & G24 Recessed FG-BG GaN HEMT ,G14 Recessed FG-BG GaN HEMT

It resulted in increased drain conductance ( $G_D$ ) of 2.5(S/mm) appeared for the proposed structure. Tables 4, and 5 show the Electrical properties and physical properties of GaN in comparison with other available materials. This elevated differentiation shows the advantages of GaN which is used in constructing the proposed model to produce the novel structure.

The methods used in the simulation of all structures are presented here in Table 6. In Table 7 models required for the simulation for the proposed device are models required illustrated. Table 8 contains the final obtained results for the various structures like Multi gate field plated (MGFP), Discrete field plate (DFP), Gate field plate (GFP), Camel shaped gate HEMT, Gama field plate (GFP), Camel shaped gate, Gama shaped gate HEMT, proposed structure for asymmetric high K dielectric

| <b>TABLE 4.</b> Electrical Properties of AlGaN, GaN Material | TABLE 4 | Electrical | Properties of | f AlGaN. | GaN Materials |

|--------------------------------------------------------------|---------|------------|---------------|----------|---------------|

|--------------------------------------------------------------|---------|------------|---------------|----------|---------------|

| Characteristics                            | Gallium<br>Nitride | Aluminum<br>Gallium<br>Nitride |

|--------------------------------------------|--------------------|--------------------------------|

| Saturation Velocity of electrons (cm/s)    | 2.5E7              | 11E7                           |

| Valance Band DOS (cm <sup>-3</sup> )       | 2.51E18            | 2.06E18                        |

| The affinity of Electron (EV)              | 4                  | 3.411                          |

| Mobility of Electron (cm <sup>2</sup> /vs) | 900                | 300                            |

| Conduction Band DOS (cm <sup>-3</sup> )    | 2.2318             | 2.718                          |

**TABLE 5.** Electrical and physical properties of Si, GaN,4H

SiC, GaAs

| Property                                        | GaAs | Si   | GaN | 4H SiC |

|-------------------------------------------------|------|------|-----|--------|

| Energy band (Ev)                                | 1.4  | 1.12 | 3.2 | 3.4    |

| Thermal conductivity (W/cm/K)                   | 0.5  | 1.5  | 4.9 | 1.3    |

| Dielectric constant, E                          | 13.1 | 11.8 | 9.7 | 9.5    |

| Electron mobility(cm <sup>2</sup> /vs)          | 6000 | 1350 | 900 | 1300   |

| Saturation velocity Vsat (10 <sup>7</sup> cm/s) | 1.3  | 1    | 2   | 3      |

| Critical field $E_{CF}$ (MV/cm)                 | 0.4  | 0.25 | 3   | 4      |

TABLE 6. Methods used for simulation of Device Even power

| Methods        | Interpretation                                                                               |

|----------------|----------------------------------------------------------------------------------------------|

| Taun           | Used in interface defect level electron concentration lifetime                               |

| Taup           | Used in interface defect level hole concentration lifetime                                   |

| f. conmun      | Indicates composition, temperature, and electron models which depend on doping functionality |

| Material align | Specifies the fraction of the difference joining material                                    |

**TABLE 7.** Model used for simulation of the device

Model

Interpretation

| Bgn     | Indicates Bandgap narrowing. Composition, temperature, and doping-dependent bandgap narrowing. |

|---------|------------------------------------------------------------------------------------------------|

| Fldmob  | Used for a model for lateral electric field                                                    |

| Inif    | Al voltage is reset and initiated from zero                                                    |

| Gummel  | It represents a numerical solution technique                                                   |

| Vsatmod | The velocity of saturation model for the mobility of electron                                  |

Front gate (FG) and Back gate (BG) caped recessed with Dual floating material GaN HEMT resulted in best results compared to other existing results. High drain current, High transconductance, High drain conductance,

TABLE 8. Comparison of existing Transistors and Proposed structure

| Gate Shape                  | MGFT     | DFP      | GFP      | Camel | Gama  | Т     | Pi       | SG-P     | DG P     | DGT TP   | Proposed<br>Structure |

|-----------------------------|----------|----------|----------|-------|-------|-------|----------|----------|----------|----------|-----------------------|

| (L <sub>g</sub> ) nm        | 20       | 20       | 20       | 20    | 20    | 20    | 6        | 6        | 6        | 6        | 6                     |

| I <sub>on</sub> (A/mm)      | 2E-2     | 5E-2     | 5.5E-2   | 7E-2  | 1     | 2     | 4        | 4.4      | 4.6      | 4.9      | ٧,٥                   |

| I <sub>off</sub> (A) (E-11) | 360      | 250      | 60.2     | 47    | 43.2  | 18    | 8.65     | 1        | 2.63E-1  | 5.6E-2   | 8E-4                  |

| $I_{on}\!/I_{off}(E{+}8)$   | 5.56E-05 | 2.00E-04 | 9.14E-04 | 0.001 | 0.02  | 0.1   | 4.62E-01 | 4.40E+00 | 1.75E+01 | 8.75E+01 | 0.93E+4               |

| f <sub>max</sub> (GHz)      | 38       | 50       | 65       | 80    | 100   | 425   | 485      | 490      | 500      | 520      | 745                   |

| $f_{T}\left( GHz\right)$    | 14       | 18       | 40       | 60    | 90    | 310   | 400      | 537      | 540      | 560      | 743                   |

| $g_m(S/mm)$                 | 0.098    | 0.217    | 0.297    | 0.327 | 0.501 | 0.9   | 1.51     | 1.45     | 1.72     | 2.7      | 4.8                   |

| V <sub>th</sub> (V)         | -1       | -1       | -1       | -1.4  | -1.5  | -2.8  | -3.7     | -3.76    | -3.8     | -4       | -4.3.                 |

| g <sub>d</sub> (S/mm)       | 0.084    | 0.091    | 0.095    | 0.098 | 0.116 | 0.148 | 0.353    | 0.456    | 0.534    | 0.657    | 2.5                   |

| $R_{on}(\Omega mm)$         | 3.8      | 3.6      | 2.5      | 1.8   | 1.5   | 1     | 0.8      | 0.75     | 0.7      | 0.6      | 0.12                  |

Low On-Resistance, High cut off frequency, High maximum oscillation frequency ( $f_{max}$ ), low leakage current, and High  $I_{on}/I_{off}$  are obtained. With these obtained results further, it can be applied to suitable application.

AlGaN/GaN material exhibits high breakdown voltage and high electron mobility, with this property device can be applied for high frequency and high-power applications.

GaN possess high saturation velocity and high twodimensional electron Gas density at the two-layer hetero interference due to this reason GaN is consider as important candidate with high power switching transistor for future nano world. This hetero combination exhibits excellent power handling capabilities. Carrier confinement is improved by introducing increased Al mole fraction in AlGaN.

Gallium Nitride High Electron Mobility Transistor provides higher power density, small passive component, higher efficiency. GaN is feasible in both vertical and lateral structure. For high power modules vertical GaN devices are used whereas for high frequency and medium power application lateral GaN are used. Only lateral GaN are in availability and are in current trend. The drawback of GaN cascade includes packing complexity when two devices are connected in series, parasitic inductance affects switching performance of the device. The device includes low Cgd gate to drain capacitance and Cgs gate to source capacitance. Due to this reason total gate charge is smaller for GaN based switch. As switching speed is directly proportional to total gate change high switching speed is efficiency is realized for GaN HEMT. For high power electric Devices GaN is prominently implemented due to its unique features such as high thermal stability and large conduction band discontinuities, high saturation drift. The thermal conductivity is lower than

Silicon and Silicon carbide. This Silicon nature tends to higher thermal resistance leads to higher operation temperature for same dissipated power.

## 4. CONCLUSION

Asymmetric high K dielectric front gate and back gate (BG) with recessed gates, dual triple tooth metal for 6nm HEMT are proposed in this paper and its performance is analyzed for obtaining optimized results. The proposed structure is collated with a few existing HEMT structures. The DC characteristics and RF characteristics are sorted out and reported improved increased drain current (Ion) of 7.5(A/mm), low leakage current(I<sub>off</sub>) 3E-15 (A), Transconductance (Gm) of 4.8(S/mm), Drain Conductance (Gd) of 2.5(S/mm), Cutoff frequency( $f_T$ ) of 743 GHz Maximum Oscillation frequency ( $F_{max}$ ) 745 GHz, Minimum Threshold Voltage (Vth) of -4.5V, On Resistance (Ron)of 0.12(Ohms) at V<sub>gs</sub> =0V. The dominant characteristics of the proposed device aid to apply in millimeters wave application.

#### **5. REFERENCES**

- Sehra, K., Kumari, V., Gupta, M., Mishra, M., Rawal, D. and Saxena, M., "Optimization of π–gate algan/aln/gan hemts for low noise and high gain applications", *Silicon*, (2020), 1-12. https://doi.org/10.1007/s12633-020-00805-7

- Augustine Fletcher, A. and Nirmal, D., "A survey of gallium nitride hemt for rf and high power application", *Superlattice Microst*, Vol. 109, (2017), 519-537. https://doi.org/10.1016/j.spmi.2017.05.042

- Micovic, M., Brown, D., Kurdoghlian, A., Santos, D., Grabar, B., Magadia, J., Khalaf, I., Tai, H., Prophet, E. and Burnham, S., "Gan dhfets having 48% power added efficiency and 57% drain

efficiency at \$ v \$-band", *IEEE Electron Device Letters*, Vol. 38, No. 12, (2017), 1708-1711. doi: 10.1109/LED.2017.2763940.

- Jazaeri, F., Shalchian, M. and Sallese, J.-M., "Transcapacitances in epfl hemt model", *IEEE Transactions on Electron Devices*, Vol. 67, No. 2, (2019), 758-762. doi: 10.1109/TED.2019.2958180.

- Rastogi, G., Kaneriya, R., Sinha, S. and Upadhyay, R., "Optimization of ohmic contact fabrication for al0. 3ga0. 7n/aln/gan hemts on 6h-sic using recess etching and surface plasma treatment processes", *Journal of Nanomaterials & Molecular Nanotechnology*, Vol. 8, (2019), 2. https://doi.org/10.4172/2324-8777.1000267

- Kaneriya, R., Rastogi, G., Basu, P., Upadhyay, R. and Bhattacharya, A., "Intersubband device modeling of gallium nitride high electron mobility transistor for terahertz applications", *Radio Science*, Vol. 54, No. 12, (2019), 1172-1180. https://doi.org/10.1029/ 2019RS006844

- Shur, M., Gaska, R., Khan, A. and Simin, G., "Wide band gap electronic devices", in Proceedings of the Fourth IEEE International Caracas Conference on Devices, Circuits and Systems (Cat. No. 02TH8611), IEEE. (2002), D051-D051.

- Yadav, R. and Dutta, A.K., "A new charge-based analytical model for the gate current in gan hemts", *IEEE Transactions on Electron Devices*, Vol. 69, No. 4, (2022), 2210-2213. doi: 10.1109/TED.2022.3149460.

- Van Hove, M., Boulay, S., Bahl, S.R., Stoffels, S., Kang, X., Wellekens, D., Geens, K., Delabie, A. and Decoutere, S., "Cmos process-compatible high-power low-leakage algan/gan mishemt on silicon", *IEEE Electron Device Letters*, Vol. 33, No. 5, (2012), 667-669. doi: 10.1109/LED.2012.2188016.

- Selvaraj, S.L., Suzue, T. and Egawa, T., "Breakdown enhancement of algan/gan hemts on 4-in silicon by improving the gan quality on thick buffer layers", *IEEE Electron Device Letters*, Vol. 30, No. 6, (2009), 587-589. doi: 10.1109/LED.2009.2018288.

- Shen, L., Heikman, S., Moran, B., Coffie, R., Zhang, N.-Q., Buttari, D., Smorchkova, I., Keller, S., DenBaars, S. and Mishra, U., "Algan/aln/gan high-power microwave hemt", *IEEE Electron Device Letters*, Vol. 22, No. 10, (2001), 457-459. doi: 10.1109/55.954910.

- Purnachandra Rao, G., Lenka, T.R., Singh, R., Boukortt, N.E.I., Sadaf, S.M. and Nguyen, H.P.T., "Comparative study of iiinitride nano-hemts on different substrates for emerging highpower nanoelectronics and millimetre wave applications", *Journal of Electronic Materials*, Vol. 52, No. 3, (2023), 1948-1957. https://doi.org/10.1007/s11664-022-10145-4

- Wang, W., Yu, X., Zhou, J., Chen, D., Zhang, K., Kong, C., Kong, Y., Li, Z. and Chen, T., "Improvement of power performance of gan hemt by using quaternary inalgan barrier", *IEEE Journal of the Electron Devices Society*, Vol. 6, (2018), 360-364. doi: 10.1109/JEDS.2018.2807185.

- Palacios, T., Chini, A., Buttari, D., Heikman, S., Chakraborty, A., Keller, S., DenBaars, S.P. and Mishra, U.K., "Use of doublechannel heterostructures to improve the access resistance and linearity in gan-based hemts", *IEEE Transactions on Electron Devices*, Vol. 53, No. 3, (2006), 562-565. doi: 10.1109/TED.2005.863767.

- Zhang, K., Kong, C., Zhou, J., Kong, Y. and Chen, T., "Highperformance enhancement-mode Al<sub>2</sub>O<sub>3</sub>/inalgan/gan mos highelectron mobility transistors with a self-aligned gate recessing technology", *Applied Physics Express*, Vol. 10, No. 2, (2017), 024101. doi: 10.7567/APEX.10.024101.

- Hwang, I.H., Eom, S.K., Choi, G.H., Kang, M.J., Lee, J.G., Cha, H.Y. and Seo, K.S., "High-performance e-mode algan/gan mishemt with dual gate insulator employing sion and hfon", *Physica status solidi (a)*, Vol. 215, No. 10, (2018), 1700650. https://doi.org/10.1002/pssa.201700650

- Zhuge, J., Wang, R., Huang, R., Zhang, X. and Wang, Y., "Investigation of parasitic effects and design optimization in silicon nanowire mosfets for rf applications", *IEEE Transactions* on Electron Devices, Vol. 55, No. 8, (2008), 2142-2147. doi: 10.1109/TED.2008.92627.

- 18. Sehra, K., Kumari, V., Nath, V., Gupta, M. and Saxena, M., "Optimization of asymmetric  $\pi$  gate hemt for improved reliability & frequency applications", in 2019 IEEE 9th International Nanoelectronics Conferences (INEC), IEEE. (2019), 1-4.

- Sun, W., Joh, J., Krishnan, S., Pendharkar, S., Jackson, C.M., Ringel, S.A. and Arehart, A.R., "Investigation of trap-induced threshold voltage instability in gan-on-si mishemts", *IEEE Transactions on Electron Devices*, Vol. 66, No. 2, (2019), 890-895. doi: 10.1109/TED.2018.2888840.

- Lee, J.-W., Kuliev, A., Kumar, V., Schwindt, R. and Adesida, I., "Microwave noise characteristics of algan/gan hemts on sic substrates for broad-band low-noise amplifiers", *IEEE Microwave and Wireless Components Letters*, Vol. 14, No. 6, (2004), 259-261. doi.

- Shinohara, K., Corrion, A., Regan, D., Milosavljevic, I., Brown, D., Burnham, S., Willadsen, P., Butler, C., Schmitz, A. and Wheeler, D., "220ghz f t and 400ghz f max in 40-nm gan dhhemts with re-grown ohmic", in 2010 International Electron Devices Meeting, IEEE. (2010), 30.31. 31-30.31. 34.

- Lin, J., Antoniadis, D.A. and del Alamo, J.A., "Impact of intrinsic channel scaling on ingaas quantum-well mosfets", *IEEE Transactions on Electron Devices*, Vol. 62, No. 11, (2015), 3470-3476.

- Sharma, N., Mishra, S., Singh, K., Chaturvedi, N., Chauhan, A., Periasamy, C., Kharbanda, D.K., Parjapat, P., Khanna, P. and Chaturvedi, N., "High-resolution algan/gan hemt-based electrochemical sensor for biomedical applications", *IEEE Transactions on Electron Devices*, Vol. 67, No. 1, (2019), 289-295. doi: 10.1109/TED.2019.2949821.

- Balaji, B., Srinivasa Rao, K., Girija Sravani, K., Bindu Madhav, N., Chandrahas, K. and Jaswanth, B., "Improved drain current characteristics of hfo2/sio2 dual material dual gate extension on drain side-tfet", *Silicon*, (2022), 1-6. https://doi.org/10.1007/s12633-022-01955-6

- Gowthami, Y., Balaji, B. and Rao, K.S., "Design and performance evaluation of 6nm hemt with silicon sapphire substrate", *Silicon*, (2022), 1-8. https://doi.org/10.1007/s12633-022-01900-7

- Kumar, P.K., Balaji, B. and Rao, K.S., "Performance analysis of sub 10 nm regime source halo symmetric and asymmetric nanowire mosfet with underlap engineering", *Silicon*, Vol. 14, No. 16, (2022), 10423-10436. https://doi.org/10.1007/s12633-022-01747-y

- Balaji, B., Rao, K.S., Sravani, K.G. and Aditya, M., "Design, performance analysis of gaas/6h-sic/algan metal semiconductor fet in submicron technology", *Silicon*, (2022), 1-5. https://doi.org/10.1007/s12633-021-01545-y

- Balaji, B., Rao, K.S., Aditya, M. and Sravani, K.G., "Device design, simulation and qualitative analysis of gaasp/6h-sic/gan metal semiconductor field effect transistor", *Silicon*, Vol. 14, No. 14, (2022), 8449-8454. https://doi.org/10.1007/s12633-022-01665-z

- Chen, C.-H., Krishnamurthy, K., Keller, S., Parish, G., Rodwell, M., Mishra, U. and Wu, Y.-F., "Algan/gan dual-gate modulationdoped field-effect transistors", *Electronics Letters*, Vol. 35, No. 11, (1999), 933-935. doi: 10.1049/el:19990627.

- He, J., Cheng, W.C., Wang, Q., Cheng, K., Yu, H. and Chai, Y., "Recent advances in gan-based power hemt devices", *Advanced Electronic Materials*, Vol. 7, No. 4, (2021), 2001045. doi: 10.1002/aelm.202001045.

- Latorre-Rey, A.D., Albrecht, J.D. and Saraniti, M., "Generation of hot electrons in gan hemts under rf class a and ab pas", in 2017

75th Annual Device Research Conference (DRC), IEEE. (2017), 1-2.

- 32. Zhang, N.-Q., Moran, B., DenBaars, S., Mishra, U., Wang, X. and Ma, T., "Effects of surface traps on breakdown voltage and switching speed of gan power switching hemts", in International Electron Devices Meeting. Technical Digest (Cat. No. 01CH37224), IEEE. (2001), 25.25. 21-25.25. 24.

- Ambacher, O., Smart, J., Shealy, J., Weimann, N., Chu, K., Murphy, M., Schaff, W., Eastman, L., Dimitrov, R. and Wittmer, L., "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in n-and ga-face algan/gan

heterostructures", *Journal of Applied Physics*, Vol. 85, No. 6, (1999), 3222-3233. https://doi.org/10.1063/1.369664

- Mishra, U.K., Shen, L., Kazior, T.E. and Wu, Y.-F., "Gan-based rf power devices and amplifiers", *Proceedings of the IEEE*, Vol. 96, No. 2, (2008), 287-305. doi: 10.1109/JPROC.2007.911060.

- Arulkumaran, S., Egawa, T., Selvaraj, L. and Ishikawa, H., "On the effects of gate-recess etching in current-collapse of different cap layers grown algan/gan high-electron-mobility transistors", *Japanese Journal of Applied Physics*, Vol. 45, No. 3L, (2006), L220. doi: 10.1143/JJAP.45.L220.

#### **COPYRIGHTS**

©2023 The author(s). This is an open access article distributed under the terms of the Creative Commons Attribution (CC BY 4.0), which permits unrestricted use, distribution, and reproduction in any medium, as long as the original authors and source are cited. No permission is required from the authors or the publishers.

#### Persian Abstract

چکیدہ

تاثیر اسپیسر نیترید آلومینیوم (AIN)، لایه درپوش نیترید گالیم (GaN)، دروازه P جلو (GP)و دروازه P پشت (BB)، مواد شناور دو گانه مواد دی الکتریک با K بالا مانند دی اکسید هافنیوم (HfO2)، اکسید آلومینیوم (Al2O3)، نیترید سیلیکون (Ai3N)بر روی نیترید گالیم آلومینیوم/ نیترید گالیم (AlGaN/GaN)، ترانزیستور متحرک الکترون بالا (HEMT) با فناوری ۲ نانومتری شبیه سازی شده و نتایج با استفاده از طراحی به کمک رایانه فناوری (TCAD) کالامان Silvaco Atlas (TCAD) و Alas (Sign)، نیترید معاطعه قرار گرفت. لایه های درپوش Ala، Al استخراج شده است. ابزار. اهمیت مواد دی الکتریک با پتاسیم بالا مانند Old و Al2O3 برای پیشنهاد Gan HEMT مورد مطالعه قرار گرفت. لایه های درپوش Ala، Al مواد دی الکترون داغ توسط برای غلبه بر عقبنشینی های معمولی ترانزیستور مانند نقصهای سطحی، پراکندگی الکترون، و تحرک کمتر الکترون، روی یکدیگر لایه بندی می شوند. اثر الکترون داغ توسط گیت نوع P غلبه می کند. مواد شناور دندان سه گانه در لایه بافر قرار می گیرد تا ولتاژ شکست را بهبود بخشد. بنابراین، با بهینهسازی ساختار HEMT، ناتوانی های دستگاههای گیت نوع P غلبه می کند. مواد شناور دندان سه گانه در لایه بافر قرار می گیرد تا ولتاژ شکست را بهبود بخشد. بنابراین، با بهینهسازی ساختار HEMT، ناتوانیهای دستگاههای بالا، مواد دندانه سه گانه دولایه بافر دندان سه گانه در لایه بافر قرار می گیرد تا ولتاژ شکست را بهبود بخشد. بنابراین، با بهینهسازی ساختار HEMT، ناتوانیهای دستگاههای بالا، مواد دندانه سه گانه دولایه بافر با گیت فرورفته یا محلی (GA) به دلیل لایه های درپوش GAN، گیت چندگانه (GA های دورانه دورانه دور قورا GP)، و مواد دی الکتریک با A بالا، مواد دندانه سه گانه دوگانه در لایه بافر با گیت پی مور HEMT غیرفعال شده تک گیت GB. (GA) و مواد دی الکتریک با HEMT بالا، مواد دندانه سه گانه دولانه با گیت فرورفته ایجاد شده است. مقایسه بیشتر HEMT غیرفعال شده تک گیت (GA)، برین دروازه (GP) او و رو گیت (GA) فیرفعال شده دی ایکتریک با A بابقارن دروازه (GP) و گیت پی عقب (GB)، جلوی دی الکتریک با A بالا نامتقارن دروازه (GP) و گیت (GA) فیرفعال شده دندانه سه گانه (DG)، گیت و GA)، و وی تو تو GA)، جلوی دی الکتریک با A بالا نامتواری دروازه (GA) و گیت پی غیرفتال بودن (GA)، میالا)، خریان ای و GA) (GA) فیر فالو می GA) فی