# International Journal of Engineering

Journal Homepage: www.ije.ir

# Modified Second Order Generalized Integrator-frequency Locked Loop Grid Synchronization for Single Phase Grid tied System Tuning and Experimentation Assessment

### B. Brahmbhatt\*a, H. Chandwanib

<sup>a</sup> Electronics and Communication Department, Government Engineering Collage,Modasa,Gujarat, India <sup>b</sup> Electrical and Electronics Department, The Maharaja Sayajirao University of Baroda,Vadodara,Gujarat,India

PAPER INFO

# ABSTRACT

Paper history: Received 03 May 2020 Received in revised form19 October 2021 Accepted 27 October 2021

Keywords: Phase-locked Loop Frequency Lock Loop STM32F407VG Microcontroller DC-Signal Cancellation Block

The phase-locked loop (PLL) is applied in grid-tied systems to synchronise converter operation with grid voltage, affecting converter stability and performance. Synchronous reference frame PLL (SRF-PLL) is a popular grid synchronisation method due to its simplicity and reliability. Normal SRF-PLL cannot suppress DC offset, causing basic frequency and phase oscillations. When a grid is irregular, its bandwidth should be reduced to ensure acceptable disturbance rejection without sacrificing detection speed. To enhance the phase-angle estimation speed and accuracy, the researchers modified structure by adding the pre/in-loop filter in advanced PLLs. The capacity to deliver improved dynamic response and reduced settling time without compromising system stability or the ability to eliminate disturbances is a major issue for PLLs. Among different control methods, SOGI-FLL (second-order generalised integrator-based frequency locked loop) had the best performance. It tracks grid voltage frequency precisely even when there is harmonics, voltage variations, frequency fluctuations, etc. In the event of a dc offset, the calculated frequency incorporates low frequency oscillations. A modified second-order generalised integrator frequency-locked loop (MSOGI-FLL) is presented in this work to address grid voltage anomalies of all types, including dc offset. Using the Waijung Block-set of MATLAB/Simulink, a Modified SOGI-FLL is realized and evaluated by applying abnormal grid voltage situations using a low-cost DSP-based STM32F407VGT microcontroller. The results demonstrate MSOGI-better FLL's performance in harsh circumstances.

doi: 10.5829/ije.2022.35.02b.03

## 1. INTRODUCTION

Many grid-connected inverters have drawn interest for their economical circuit architecture and advanced control techniques due to the rapid rise in renewable energy [1]. The phase-locked loop (PLL) is an important component in the grid assisted inverter's control strategy since it is primarily utilised to keep the inverter and grid synchronised. A new energy power system's security and stability are directly associated with the performance of the grid-connected inverter [2]. For the converter to work properly, the control

\*Corresponding Author Email <u>bhavic0072009@gmail.com</u> (B. Brahmbhatt) algorithm must accurately compute the amplitude, phase-angle, and frequency from the grid voltages. It is grid difficult when the voltage has irregularities(frequency variation, harmonics, voltage fluctuation, dc offset, and/or distortion, switching notches, etc.) [2]. These anomalies can cause measurement and data translation mistakes, making predicting frequency and synchronisation problematic [3]. A phase-locked loop is composed of a phase detector, a filter, and a voltage-regulated oscillator. The PD controls the gain of a voltage-regulated oscillator, whose output signal is frequency and phase synced with the input reference signal. Golestan et al. [3, 4] addressed the categorization of phase lock loop with varying phase detector. Under distorted grid signal

Please cite this article as: B. Brahmbhatt, H. Chandwani, Modified Second Order Generalized Integrator-frequency Locked Loop Grid Synchronization for Single Phase Grid tied System Tuning and Experimentation Assessment, *International Journal of Engineering, Transactions B: Applications* Vol. 35, No. 02, (2022) 283-290 circumstances, PD structures based on generalised integrators (GI) function better and are more reliable [4, 5]. Thus, SOGI-PLL is better than other PLL designs [3-5]. It works quickly and accurately in bad grid circumstances. In contrast to SOGI-PLL, where the estimated frequency is utilized as feedback from the SOGI-OSG block, SOGI-FLL use a frequency-locked loop (FLL) to adaptively get the frequency [6]. The adaptive nature prevents PLL and improves including Factors performance. transformer nonlinearity, A/D conversion error, analogue device anomalous temperature, and zero drift all produce DC offset when the power grid failure occurs [7, 8]. There are several ways to reduce the DC offset in SRF-PLL nowadays. Golestan et al. [9] suggested a cascaded second-order generalised integrator-phase lock loop (CSOGI-PLL) to eliminate the DC quantity; however, it comprises se Factors including transformer nonlinearity, A/D conversion error, analogue device anomalous temperature, and zero drift all produce DC offset when the power grid failure occurs. It utilizes several SOGI structures, thus the added computing cost is significant [10]. To speed up DC offset removal, Kulkarni et al. [10] devised a cascade delay signal cancellation PLL technique (CDSC-PLL), while Parag et al. [11] utilised an adaptive filter delay signal cancellation-PLL (APF-DSC-PLL) to increase the speed of DC offset rejection, but the complex structure reduces the dynamic performance of the system. Moreover, a phase-locked loop based on the modified delay signal cancellation-PLL was presented by Li et al. [12] which can enhance dynamic performance by reducing DC offset, but it would induce phase deviation, which necessitates design correction. These notch filter (NF) based on PLL and dq-DSC -PLL, as well as five additional approaches for eliminating the DC offset in the PLL. However, these phase detection approches suffer from a sluggish dynamic performance [13-15]. These approaches have the potential to increase dynamic performance while overcoming the drawbacks of conventional low-pass filters [9-16]. However, selecting and calculating the sliding window width is time-consuming [15, 16]. Thus, a modified SOGI-FLL (MSOGI-FLL) for single-phase systems is suggested to reduce frequency estimation errors caused by DC quantity and other grid irregularities (e.g. harmonics, frequency fluctuation, magnitude variation). Using the third integrator as a DC offset cancellation block, the proposed MSOGI-FLL estimates the DC offset without influencing frequency estimation in the FLL. The better performance of this structure has been demonstrated through modelling and experimental findings. The next sections describe the MSOGI-FLL and its performance under various situations.

## 2. ORGANIZATION & TRANSFER FUNCTION: SECOND-ORDER GENERALIZED INTEGRATOR (SOGI)-FREQUENCY LOCKED LOOP(FLL)

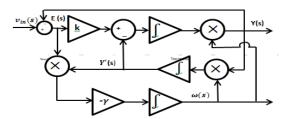

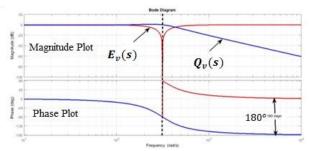

SRF based PLL uses an additional voltage-controlled oscillator, although SOGI-QSGs serve as filters as well as voltage-controlled oscillators. The SOGI resonator's centre frequency is adjusted to match the input frequency using an auto tune block, as shown in Figure 1. The Frequency-Locked Loop (FLL) block estimates the frequency adaptively by changing the gain ( $\Gamma$ ) in SOGI-FLL, thus the PLL block used in SOGI-PLL is omitted. The SOGI-FLL works far better, faster, and more accurately than traditional SRF-PLL-based systems in grid anomalies including harmonics, voltage variations, frequency fluctuations, and phase jump etc. for instance. The transfer functions of band-pass filter (BPF) and low-pass filter (LPF) illustrated in Equations (1) and (2) are derived from the conventional SOGI-QSG in Figure 1. A real positive value of gain k can be tuned to alter the bandpass filter  $D_{SOGI-FLL}$  and lowpass filter  $Q_{SOGI-FLL}(s)$  bandwidth (or sharpness). This means that the signals Y(s) and Y'(s) are the BPF and LPF outputs, with a 90° phase difference (as shown in bode diagram, Figure 2), respectively. In reality, the LPF outperforms the BPF when it comes to highfrequency filtering. The output signal (Y'(s)) of SOGI-QSG is badly affected by a non-zero dc offset in the measured grid voltage.

$D_{SOGI-FLL}(s)$  and  $Q_{SOGI-FLL}(s)$  have the following transfer functions:

$$D_{SOGI-FLL}(s) = \frac{Y(s)}{v_{in}(s)} = \frac{k \ s \ \omega}{s^2 + k\omega s + \ \omega^2}$$

(1)

$$Q_{SOGI-FLL}(s) = Q_v(s) = \frac{Y'(s)}{v_{in}(s)} = \frac{k\,\omega^2}{s^2 + k\omega s + \,\omega^2}$$

(2)

Furthermore, Bode's magnitude responses retain 0 dB at the 50Hz fundamental frequency while attenuating amplitude at the 5th and 7th harmonic frequencies of 250Hz and 350Hz, respectively. It should react as a notch filter with zero gain and 180° phase leap at centre frequency to produce auto-tunable SOGI-QSG (see Figure 3).

The transfer function of voltage error signal  $\mathbf{E}_{SOGI-FLL}$  can be described as:

$$E_{\text{SOGI-FLL}}(s) = E_{\nu}(s) = \frac{\varepsilon_{\nu(s)}}{v_{\text{in}(s)}} = \frac{s^2 + \omega^2}{s^2 + k\omega s + \omega^2}$$

(3)

In the SOGI-FLL, a frequency error signal  $(\varepsilon_f)$  is generated from the product of  $E_{SOGI-FLL}(s)$  &  $Q_{SOGI-FLL}(s)$ . As illustrated in Figures 1 and 3, the frequency locking loop may be built utilising the

Figure 1. The fundamental architecture SOGI -FLL

Figure 2. Bode Graph of (a)  $D_{SOGI-FLL}(s)$ , and (b)  $Q_{SOGI-FLL}(s)$  with various value of k

Figure 3. Bode Graph of the  $E_{SOGI-FIL}(s)$  &  $Q_{SOGI-FIL}(s)$  in an SOGI-QSG

frequency error signal  $(\varepsilon_f)$  and a negative controller gain $(-\gamma)$  of frequency loop. The SOGI resonance frequency $(\omega')$  is changed until it equals the input frequency  $(\omega)$  using the frequency loop controller gain  $(-\gamma)$ . A feed-forward variable,  $\omega_c$ , is included in the FLL to accelerate initial synchronisation. By incorporating feedback, a value of  $\gamma$  should be normalised and defined as follows:

$$\gamma = \frac{k\omega}{v^2} \Gamma \tag{4}$$

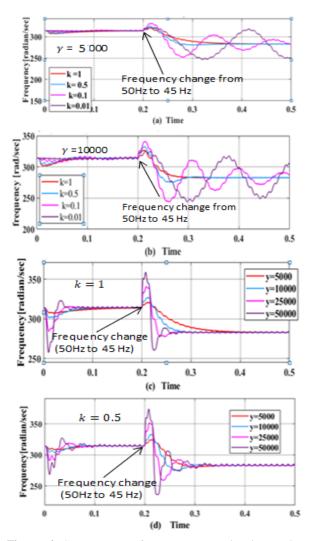

With a feed-forward of  $2\pi * 50$ , the dynamic response of frequency estimationin SOGI-FLL is studied. As observed the dynamic response of frequency estimation in Figures 4(a), 4(b), 4(c) and 4(d) using progressive values of k and constant values of  $\gamma$ , and vice versa. Table 1 contains the evaluation of parameter k and  $\gamma$  for SOGI-FLL, as shown in Figure 4 (a)-(d). Transient responsiveness and bandwidth of SOGI-FLL are affected by the para-meter k. The choice of gain k compromises between good signal filtering and transient response of system dynamic responsiveness (Figure 4). The choice of value  $\gamma$  compromises frequency estimate precision and SOGI-FLL dynamics. Reduction in a bandwidth increases rise time ( $t_{rise} = 0.35$ / BW), but improves other metrics.

### 3. STRUCTURE & TRANSFER FUNCTIONS : MSOGI-FLL

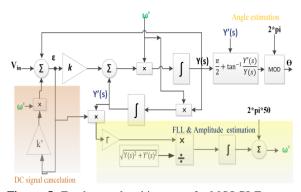

Figure 5 depicts the SOGI-FLL's fundamental structure.

When the third integrator estimates the DC offset, it subtracts it from the signal to improve the system's DC offset rejection capabilities. In addition, Figure 5 shows suggested MSOGI-FLL the structure, which incorporates a DC signal cancellation (DSC) block and a SOGI-FLL structure. In general, a DC-offset can be introduced into the grid signal by the signal conditioning or measuring equipment, as well as other factors like half-wave rectification. Because of this, the pre-filtering stage includes a DC signal cancellation (DSC) block that provides excellent DC-offset and SOGI-FLL rejects the rejection low-order harmonic.

A new version of the band-pass SOGI-FLL (Figure 5) filter [17-19] designated as MSOGI-FLL can be proposed by including the DSC operator. A grid signal polluted with a DC-offset, MSOGI transfer functions is represented as follows for comprehension purposes:

$$D_{MSOGI-FLL}(s) = \frac{Y(s)}{v_{in}(s)} = \frac{k\omega' s^2}{s^3 + k\omega'^{s^2} + k'\omega'^{s^2} + \omega'^2 s + k'\omega'^3}$$

(5)

Figure 5. Fundamental architecture of a MSOGI-Frequency lock loop

**Figure 4.** Step response for Frequency Estimation: various values for kand Constant Values (a)  $\gamma$ =5000,(b)  $\gamma$ =10000, (c) &(d)various value of  $\gamma$  and constant value k=1, and k=0.5, respectively

TABLE 1. Evaluation of parameter for SOGI-FLL

| Parameter | Variation<br>r in<br>parameter |        | Steady-<br>state<br>response | recoonce  | Settlement<br>time |

|-----------|--------------------------------|--------|------------------------------|-----------|--------------------|

| k         | Increase ↑                     | Worthy | Worthy                       | Worthy    | Reducing           |

|           | Decrease↓                      | Poor   | Poor                         | Poor      | Increasing         |

| γ         | Increase ↑                     | Poor   | Average                      | No change | e Reducing         |

|           | Decrease↓                      | Worthy | Good                         | No change | e Increasing       |

$$Q_{MSOGI-FLL}(s) = \frac{Y'(s)}{v_{in}(s)} = \frac{k\omega's}{s^3 + k\omega's^2 + k'\omega's^2 + \omega'^2 + k'\omega'^3}$$

(6)

$$E_{MSOGI-FLL}(s) = \frac{V_{dc}(s)}{v_{in}(s)} = \frac{k'\omega'^{s^2} + k'\omega'^3}{s^3 + k\omega's^2 + k'\omega's^2 + \omega'^2 s + k'\omega'^3}$$

(7)

Using Routh hurtiz criteria, the gain k is given as:

$$k = \frac{9.2}{\omega' t_s}; t_s = 4.6 * \tau; and \tau = \frac{1}{\zeta \omega_n}$$

(8)

In order to filter out low and high-frequency components in the input signals, gain k must be properly tuned. These graphs (see Figures 2 and 3) show that unlike  $D_{SOGI-FLL}(s)$ ,  $Q_{SOGI-FLL}(s)$  attenuates low frequency components, leaving the dc offset. The quantities k and k' are chosen from the roots of the denominator of transfer functions/characteristic equation of MSOGI- $FLL(D_{MSOGI-FLL}(s), and Q_{MSOGI-FLL}(s))$  with equal real parts (Figure 6) (all three poles have equal natural frequency of oscillation). On the other hand,  $\omega_{n1}$  $=\omega_{n2} = 2*pi*50$  rad/s (same as for tuning SOGI-FLL) is used to compute the gain k and k' respectively. The bode graphs in Figure 6 demonstrates the impact of both gain adjustments as well as performance assessment of SOGI-FLL and MSOGI-FLL using magnitude plots of transfer functions from equations [1-3] and [5-7]. Figures 6 (a) and 6(b) show magnitude bode graphs of  $D_{MSOGI-FLL}(s)$  and  $Q_{MSOGI-FLL}(s)$  (Equations 5 and 6), below 0dB for low frequency components, indicating attenuation of low frequency and DC components. It is clear that a positive gain  $Q_{SOGI-FLL}(s)$ , which does not reduce the DC signal. Due to presence of third generalised integrator, the magnitude of the transfer function is close to 0dB.  $E_{MSOGI-FLL}(s)$ Moreover,  $Q_{MSOGI-FLL}(s)$  has negative gain at frequencies over 50Hz, which reduces higher order harmonics. But it's considerably lower than 50Hz. With the third integrator component (and higher order frequencies) are greatly attenuated, leaving only the low order frequencies to pass, as seen below. It aids in estimating and eliminating the DC offset from grid voltage.

Figure 6. Bode Graph of the transfer function MSOGI-FLL and SOGI-FLL

## **4. EXPERIMENTAL RESULTS**

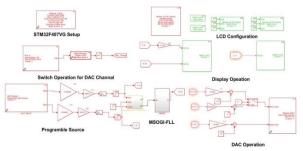

MATLAB/ Simulink is used to design and implement the MSOGI-FLL on a downscaled STM32F407VGT6 microcontroller. The discrete MSOGI-FLL model (see Figure 7) is translated to c code before being compiled and dumped into the microcontroller. Microcontroller STM32F407VGT6 has two digital analogue converters (12bit-DAC) and supports waijung environment in SIMULINK/MATLAB (i.e. model-based programming).

It is low cost and 32-bit. Simulated results back up the experimental findings, demonstrating the efficacy of MSOGI-FLL when used in model-based programming There are a few useful parameters for MSOGI-FLL: k = 0.5, k'=0.2,=-5000, sapling time ts = 300 usecond, and f g = 50 Hz for grid voltage frequency. The ADC conversion unit and other digital/discrete units introduce DC-offset, causing inaccuracy in phase estimation of SOGI-FLL.While this was going on, a slew of researchers presented new and better as well ascomplexSOGI-FLL structures of filters. Using the third integrator in MSOGI-FLL to estimate the dc offset allows for better DC offset rejection by subtracting the estimate from the signal. In the experimental setup, MSOGI-FLL is validated by testing each instance separately in the following ways:

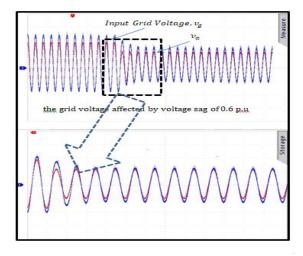

Assessment case 1: Experimentation is performed with 0.65p.u. voltage sag on the grid voltage.

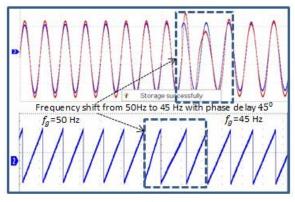

Assessment case 2: Examination are performed on grid frequency by imposing a 5% step change (i.e. frequency leap from 50Hz to 45Hz) and a phase angle shift from  $0^{\circ}$  to  $45^{\circ}$  on grid frequency and phase.

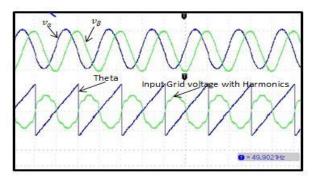

Assessment 3:grid voltage that has been subjected to harmonic distortion is used.

Figure 8 presents the experimental findings obtained to evaluate the MSOGI-FLL settling time on a grid voltage influenced by a 0.65 p.u voltage sag at Figure 8 depicts the SOGI-FLL  $v_{\alpha}/v_{in}$  settle down near to the fourth cycle, or 45 m-second, when utility voltage is influenced by a voltage drop in grid voltage. A frequency step change from 50Hz to 45Hz and a phase angle shift from  $50^{\circ}$  to  $45^{\circ}$  are applied to the grid voltage during experimental test 2, as illustrated in Figure 9. Only at t = 400m-second, as shown in Figure 8, is the phase angle shifted from  $50^{\circ}$  to  $45^{\circ}$ . Preliminary results show that the MSOGI-FLL frequency and phaseangle readings are stable, withjust a little frequency shift occurring before the third cycle is reached. This test uses a microcontroller's ADC pin to control the of a sine wave generated frequency inside MATLAB/Simulink (see Figure 7), rather than an AC grid simulator. For experimental test-3, the dynamic response of SOGI-FLL is tested by applying harmonic voltages of 3rd, 5th, and 7th order with amplitudes of 0.35p.u., 0.1p.u., and 0.08p.u. in relation to the fundamental grid voltage (as shown in Figure 10).

As illustrated in Figure 10, MSOGI-QSG is experimentally shown to be a band-pass filter for the Figure 10 shows that the SOGI-FLL is immune to distorted grid voltage. Figure 9 demonstrates that the measured phase-angle is devoid of harmonic distortion and the 100Hz phase-angle frequency component.

Figure 7. Model based programmingin STM 32F407VG using waijung blockset of MATLAB/Simulink

Figure 8. Experimental results of Test case:1. (Time Scale:20m-second/div; 0.5V/div)

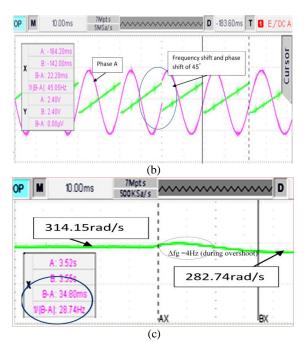

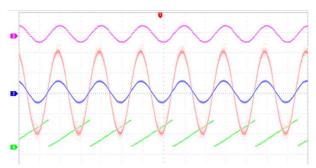

MSOGI-FLL output signals, i.e.  $v_{\alpha}/v_{in}$  and  $v_{\beta}/v_{in}$ , which are likewise devoid of harmonic distortion. Despite various irregularities affecting the grid voltage, the MSOGI-FLL continues to operate the same way. There is a single-phase voltage source converted, 10mH line inductor, auto-transformer and ARM cortex M4 microprocessor built as an experimental prototype for testing. The control algorithm was created in MATLAB/Simulink using the waijung blockset and then loaded onto a low-cost STM32F407VG ARM Cortex M4 microcontroller for general-purpose digital signal processing. Experimental results (see Figure 12) are carried out at 110V RMS grid voltage on experimental set-up (see Figure 11) at the point of common coupling. The sampling time of model base program is choosen 300micro-second. The control of single-phase grid tied inveter is developed using wellknown synchronous reference frame current control techqnique.

**Figure 9.** Experimental results of Test case:2. .(For (a)Time Scale:20m-second/div; 0.5V/div; (b) Time Scale:10m-second/div; 1V/div)

Figure 10. Experimental results of Test case:3.(Time Scale:10m-second/div; 1V/div)

Figure 11. Experimental setup of single-phase grid interfaced voltage source converter

**Figure 12.** Experimental result of single-phase grid interfaced voltage source converter(Time scale:10ms//div) : (a) $i_g$ (Pink and blue; Scale 4A/div), (b)  $i_g$ (Orage; Scale: 75V/div), and (c) theta (green)

#### **5.DISCUSSION**

Table 2 summarises the experimental findings for the single- phase grid voltage test scenarios.

It's possible to estimate the peak errors in the fundamental grid's parameters (e.g. amplitude, phase and frequency information), and tr stands for the settling time performance. The presented technique takes around 2.4 times as long to compute the grid's parameters as the current standard.

With the SOGI-OSG and DC signal cancellation block, MSOGI-FLL can achieve better immunity to DCoffset and harmonic noise. Both the SOGI-FLL and the SRF-PLL have frequency information that is impacted by the phase angle change. However, in the instance of

**TABLE 2.** Highlights of Comparative Performance Assessment

| Assessment            |                                |                     |                       |                       |  |  |

|-----------------------|--------------------------------|---------------------|-----------------------|-----------------------|--|--|

| Cases                 | Peak Errors                    | SRF-PLL             | SOGI-<br>FLL          | MSOGI-<br>FLL         |  |  |

| Voltage<br>Drops      | $\Delta A_g$                   | -                   | -                     | -                     |  |  |

|                       | $\Delta f_g$                   | -                   | -                     | -                     |  |  |

|                       | $\Delta 	heta_g$               | -                   | -                     | -                     |  |  |

|                       | $t_r$                          | ≈ 80                | ≈ 55                  | ≈ 45                  |  |  |

| Freq.Step<br>change   | $\Delta A_g$                   | ≈ 2                 | -                     | -                     |  |  |

|                       | $\Delta f_g$ (during oveshoot) | ≈ 9                 | ≈ 5                   | ≈ 4                   |  |  |

|                       | $\Delta 	heta_g$               | $\approx 5^{\circ}$ | $\approx 1.5^{\circ}$ | $\approx 1.5^{\circ}$ |  |  |

|                       | $t_r$                          | ≈ 80                | $\approx 40$          | ≈ 34                  |  |  |

| DC-Offset Elimination |                                | NO                  | NO                    | YES                   |  |  |

| Harmonics Attenuation |                                | NO                  | YES                   | YES                   |  |  |

| Steady-state Accuracy |                                | Average             | Good                  | Good                  |  |  |

| Control parameters    |                                | 2                   | 2                     | 3                     |  |  |

| PI Tunning Required   |                                | YES                 | NO                    | NO                    |  |  |

the suggested method, the predicted frequency has a maximum overshoot of 4 Hz. With a net settling time of 34 ms, the suggested single-phase system has proven to have strong harmonics elimination and DC-offset rejection capabilities. There is therefore significant potential for the suggested system to identify harmonic and fundamental grid voltage characteristics selectively.

#### 6. CONCLUSIONS

A good rejection of DC-offset, harmonics, and the frequency and phase-angle extraction may be achieved using MSOGI-FLL technique. Except for the existence of DC offset, SOGI-FLL can properly estimate the grid signal's frequency. Due to a DC offset in grid voltage, the predicted frequency has a 100Hz low frequency component. When harmonics are present, the distortion on this 100Hz ripple is amplified. The DG based inverter's synchronisation and control may be compromised as a result of this frequency estimate inaccuracy. Control parameter selection of SOGI-FLL is an art that balances the dynamic responsiveness, filtering capabilities, and required precision in detecting frequency and phase angle for single-phase grid-tied inverters under less than ideal grid circumstances. There is no ripple in the predicted synchronised frequency when using the Two essential blocks constitute the MSOGI-FLL structure: a basic SOGI-QSG architecture block modified with DC offset cancellation block, and a FLL for adaptively computing grid frequency. The dc offset cancellation block (i.e.third integrator) in MSOGI-FLL reduces the DC offset compared to the normal SOGI-FLL structure. Thus, the suggested technique is capable of rejecting DC offset and therefore correctly tracking the basic grid-voltage component frequency under all grid irregularities, in addition to the advantages of standard SOGI-FLL. In addition, the suggested systemis resistant to volatage sag/swell in the grid voltage and frequency fluctuations. Experiments results have shown that the proposed MSOGI-FLL seems to be more precise and has a superior transient stability than the conventional SOGI-FLL.

### **7.REFERENCES**

- Chishti, F., Murshid, S. and Singh, B.J.I.T. o.I.A., "Development of wind and solar based ac microgrid with power quality improvement for local nonlinear load using mlms" *IEEE Transactions on Industrial Electronics*, Vol. 55, No. 6, (2019), 7134-7145. doi: 10.1109/TIA.2019.2923575

- Kouro, S., Leon, J.I., Vinnikov, D. and Franquelo, L.G.J.I.I.E.M., "Grid-connected photovoltaic systems: An overview of recent research and emerging pv converter technology", *IEEE Industrial Electronics Magazine*, Vol. 9, No. 1, (2015), 47-61. doi: 10.1109/MIE.2014.2376976

- 290 B. Brahmbhatt and H. Chandwani / IJE TRANSACTIONS B: Applications Vol. 35, No. 02, (February 2022) 283-290

- Golestan, S., Guerrero, J.M. and Vasquez, J.C.J.I.T.o.P.E., "Single-phase plls: A review of recent advances" *IEEE Transactions on Power Electronics*, Vol. 32, No. 12, (2017), 9013-9030. doi: 10.1109/TPEL.2017.2653861

- Golestan, S., Guerrero, J.M. and Vasquez, J.C.J.I.T.o.P.E., "Three-phase plls: A review of recent advances", *IEEE Transactions on Power Electronics*, Vol. 32, No. 3, (2016), 1894-1907. doi: 10.1109/TPEL.2016.2565642

- Brahmbhatt, B. and Chandwani, H., "Single phase transformerless photovoltaic inverter with reactive power control", IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES) in 2016 IEEE. (2016), 1-5.

- He, X., Geng, H. and Yang, G.J.I.T.o.I.E., "A generalized design framework of notch filter based frequency-locked loop for threephase grid voltage", *MLMS IEEE Transactions on Industrial Electronics* Vol. 65, No. 9, (2017), 7048-7072, doi: 10.1109/tie.2017.2784413

- Santos Filho, R.M., Seixas, P.F., Cortizo, P.C., Torres, L.A. and Souza, A.F.J.I.T.o.i.e., "Comparison of three single-phase pll algorithms for ups applications", *IEEE Transactions on Industrial Electronics* Vol. 55, No. 8, (2008), 2923-2932. doi: 10.11/.9TIE.2008.924205

- Thacker, T., Boroyevich, D., Burgos, R. and Wang, F.J.I.T.o.I.E., "Phase-locked loop noise reduction via phase detector implementation for single-phase systems", *IEEE Transactions on Industrial Electronics*, Vol. 58, No. 6, (2010), 2482-2490. doi: 10.1109/TIE.2010.2069070

- Golestan, S., Guerrero, J.M. and Gharehpetian, G.B.J.I.T.o.P.E., "Five approaches to deal with problem of dc offset in phaselocked loop algorithms: Design considerations and performance evaluations", *IEEE Transactions on Power Electronics*, Vol. 31, No. 1, (2015), 648-661.doi: 10.1109/TPEL.2015.2408113

- Kulkarni, A. and John, V.J.E.P.S.R., "Design of a fast response time single-phase pll with dc offset rejection capability", *Electrical Power System Research*, Vol. 145, (2017), 35-43. doi: 10.1016/j.epsr.2016.12.023

- Kanjiya, P., Khadkikar, V. and El Moursi, M.S.J.I.T.o.I.E., "Adaptive low-pass filter based dc offset removal technique for three-phase plls", *IEEE Transactions on Industrial*

*Electronics,* Vol. 65, No. 11, (2018), 9025-9029. doi: 10.1109/tie.2018.2814015

- Li, Y., Wang, D., Ning, Y. and Hui, N.J.E.L., "Dc-offset elimination method for grid synchronisation", *Electronics Letter* Vol. 53, No. 5, (2017), 335-337. doi: 10.1049/el.2016.4570

- Wu, F., Li, X.J.I.J.o.E. and Electronics, S.T.i.P., "Multiple dsc filter-based three-phase epll for nonideal grid synchronization", *IEEE Journal Emerging Selected Topics Power Electronics*, Vol. 5, No. 3, (2017), 1396-1403. doi: 10.1109/JESTPE.2017.2701498

- Li, Y., Wang, D., Han, W., Tan, S. and Guo, X.J.I.A., "Performance improvement of quasi-type-1 pll by using a complex notch filter", *IEEE Access*, Vol. 4, (2016), 6272-6282. doi: 10.1109/ACCESS.2016.2614008

- Hui, N., Feng, Y. and Han, X.J.E.R., The International Conference on Power Engineering (ICPE 2020), Guangzhou, China,Energy Reports Science Direct" Dc offset elimination method of phase-locked loop based on novel generalized integrator", Vol. 7, (2021), 30-35. doi: 10.1016/j.egyr.2021.02.030

- Hui, N., Feng, Y. and Han, X.J.I.A., "Design of a high performance phase-locked loop with dc offset rejection capability under adverse grid condition", *IEEE Access, 2020* Vol. 8, (2020), 6827-6838. doi: 10.1109/ACCESS.2020.2963993

- Mirhosseini Moghadam, M., Tavakoli, A. and Alizadeh, B.J.I.J.o.E., "Stability analysis of ac/dc microgrids in island mode", *International Journal of Engineering, Transactions A: Basics*, Vol. 34, No. 7, (2021), 1750-1765. doi: 10.5829/ije.2021.34.07a.20

- Ardeshir, G. and Gholami, M.J.I.J.o.E., "Dual phase detector based delay locked loop for high speed applications", *International Journal of Engineering, Transactions A: Basics* Vol. 27, No. 4, (2014), 517-522. doi: 10.5829/idosi.ije.2014.27.04a.02

- Rahimi Mirazizi, H. and Agha Shafiyi, M.J.I.J.o.E., "Evaluating technical requirements to achieve maximum power point in photovoltaic powered z-source inverter", *International Journal* of Engineering, Transactions C: Aspects, Vol. 31, No. 6, (2018), 921-931. doi: 10.5829/ije.2018.31.06c.09

#### Persian Abstract

#### چکيده

حلقه قفل فاز (PLL) در سیستم های متصل به شبکه برای همگام سازی عملکرد مبدل با ولتاژ شبکه اعمال می شود که بر پایداری و عملکرد مبدل تأثیر می گذارد. قاب مرجع سنکرون (PLL (SRF-PLL) یک روش همگام سازی شبکه محبوب به دلیل سادگی و قابلیت اطمینان آن است. SRF-PLL معمولی نمی تواند آفست DC را سرکوب کند، که باعث نوسانات فرکانس و فاز اساسی می شود. وقتی یک شبکه نامنظم است، پهنای باند آن باید کاهش یابد تا از رد اختلال قابل قبول بدون کاهش سرعت تشخیص اطمینان حاصل شود. برای افزایش سرعت و دقت تخمین زاویه فاز، محققان ساختار را با افزودن فیلتر pre/in-loop در LI های پیشرفته اصلاح کردند. ظرفیت ارائه پاسخ دینامیکی بهبود یافته و کاهش زمان ته نشینی بدون به خطر انداختن پایداری سیستم یا توانایی حذف اختلالات است. یک مشکل عمده برای LI ها در بین روش های کنترل مختلف، بهبود یافته و کاهش زمان ته نشینی بدون به خطر انداختن پایداری سیستم یا توانایی حذف اختلالات است. یک مشکل عمده برای LI های پیشرفته اصلاح کردند. ظرفیت ارائه پاسخ دینامیکی زوسانات فرکانس و غیره وجود دارد، ردیایی می کند. در صورت افست می توانایی حذف اختلالات است. فرکانس ولتاژ شبکه را دقیقاً حتی زمانی که هارمونیک ها، تغییرات ولتاژ، نوسانات فرکانس و غیره وجود دارد، ردیایی می کند. در صورت افست DC، فرکانس محاسبه شده دارای نوسانات فرکانس پایین است. یک حلقه قفل فرکانس انتگرالگر تعمیمیافته مرتبه دوم (MSOGI-FLL) راین کار برای رسیدگی به ناهنجاریهای ولتاژ شبکه از همه نوع، از حمله فست DC از محقومه بلاک (WATLAB/Simulink از MATLAB/Simulink یک الو شده عملکرد به با عمال موقعیت های ولتاژ شبکه غیرعادی با استفاده از مجموعه بلاک میتی بر DSC کم هزینه تحقق و ارزیابی می شود. نتایچ نشاندهنده عملکرد بهتر AMSOGI FLL در شرایط سخت است.