# **International Journal of Engineering**

Journal Homepage: www.ije.ir

# Design and Performance Analysis of High-k Gate All Around Fin-field Effect Transistor

K. Rohith Sai, K. Girija Sravani, K. Srinivasa Rao, B. Balaji\*, V. Agarwal

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Green Fields, Vaddeswaram, Andhra Pradesh, India

#### PAPER INFO

# Paper history: Received 23 August 2023 Received in revised form 15 October 2023 Accepted 10 November 2023

Keywords: Silicon Dioxide Gate Engineering Drain Current Fin Shape Symmetric

#### A B S T R A C T

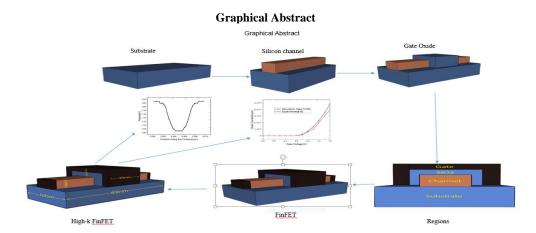

This paper introduces and investigates a symmetrical structural design centered around a Nanoscale Fin Field-Effect Transistor (Fin-FET). Employing advanced toad simulation techniques, the study discusses the characteristics of the Fin-FET. Here, a comprehensive exploration of the device performance across a spectrum of parameters, including drain current, electric field distribution, surface potential variations, energy band configurations, carrier concentration behaviors, and the Ion/Ioff ratio. Through rigorous analysis, the research sheds light on the symmetrical design's impact on these fundamental aspects of the Fin-FET's operation. The insights gained from this study hold the potential to enhance our understanding of device behavior, paving the road for refined designs and optimized utilization of Fin-FET technology in advanced semiconductor applications. Several types of engineering's are applied to test the device under various aspects. Gate engineering, doping engineering, and work function engineering were applied to test the device drain current characteristics. Therefore, this proposed has been widely adopted in modern Nano scale semiconductor devices.

doi: 10.5829/ije.2024.37.03c.04

#### **NOMENCLATURE**

| eV      | Energy bands           | SS       | Sub-threshold slope     |

|---------|------------------------|----------|-------------------------|

| $SiO_2$ | Silicon dioxide        | Ion      | On state current        |

| Ioff    | Off state current      | $I_d$    | Drain Current           |

| Vgs     | Gate to source voltage | $V_{ds}$ | Drain to source voltage |

<sup>\*</sup>Corresponding Author Email: vahividi@gmail.com (B. Balaji)

Please cite this article as: Rohith Sai K, Girija Sravani K, Srinivasa Rao K, Balaji B, Agarwal V. Design and Performance Analysis of High-k Gate All Around Fin-field Effect Transistor. International Journal of Engineering, Transactions C: Aspects. 2024;37(03):476-83.

# 1. INTRODUCTION

Last few years, the relentless demand for smaller, faster, and more energy-efficient electronic devices has driven semiconductor manufacturers to continually advance transistor technology. The traditional device such as planar metal oxide-semiconductor field-effect transistor (MOSFET) designs in the nano scale semiconductor field, which had served well for many years, faced insurmountable physical limitations as feature sizes shrank into the nanometer range. Challenges such as leakage currents, power dissipation, and gate control complexities became significant barriers to sustaining the continuous scaling predicted by Moore's Law (1).

The emergence of Fin Field-Effect Transistor (Fin-FET) technology marked a transformative moment in semiconductor design, providing a departure from the conventional planar MOSFET structure. This innovation reinvigorated the possibilities for performance scaling and energy efficiency improvements. The origin of Fin FET technology can be traced back to the early 2000s, semiconductor engineers and researchers embarked on a quest to develop new transistor designs capable of overcoming the inherent limitations of planar MOSFETs. This quest led to the concept of the Fin FET architecture, characterized by its distinctive threedimensional channel structure resembling fins. This novel architecture not only offers improved control over current flow but also effectively reduces undesirable leakage paths (2, 3). A significant milestone in the adoption of Fin FET technology was Intel's introduction of the Tri-Gate transistor in 2011. This event marked a crucial step, showcasing the practical application of Fin FETs in modern microprocessors and validating their potential to outperform traditional transistor designs. The introduction of Fin FETs has been instrumental in advancing semiconductor technology and enabling the development of more powerful and energy-efficient electronic devices (4, 5).

The operating principle of Fin FETs is deeply rooted in their distinctive structure, where the channel region is raised vertically above the substrate, resembling a fin. This structural configuration results in elevated gate control achieved by surrounding the fin with gate material. This arrangement enhances electrostatic control, leading to reduced leakage and more efficient operation. The Fin FETs offer several significant advantages, including reduced leakage currents, faster switching speeds, higher packing densities, and lower power consumption. These attributes collectively empower electronic devices with enhanced computational capabilities and energy efficiency, making them well-suited for advanced applications in consumer electronics, data centers, and emerging technologies like the Internet of Things (IoT). However, despite the transformative impact of Fin FET technology on the semiconductor industry, it is not without its challenges. The intricacies of manufacturing the intricate fin-like structures introduce complexities that could affect yields and production costs. Furthermore, as transistor dimensions continue to shrink into the nanoscale, new phenomena like quantum tunneling and variability become more prominent, necessitating innovative solutions to maintain the projected gains in performance. However, despite the transformative impact of Fin FET technology on the semiconductor industry, it is not without its challenges. The intricacies involved in manufacturing the intricate fin-like structures introduce complexities that could affect yields and production costs (6-10).

In the domain of nano-scale semiconductor technology, Fin FET have emerged as a groundbreaking solution that transcends the limitations inherent in traditional planar MOSFET designs. As transistor dimensions continue to shrink towards the nanometer scale, the challenges stemming from quantum mechanical effects, leakage currents, and power dissipation become increasingly acute (11). In response, FinFETs present an innovative three-dimensional architecture, wherein the channel takes on the form of a vertically protruding fin from the substrate. This distinctive arrangement not only enhances gate control but also effectively mitigates issues tied to short-channel effects, enabling precise modulation of current flow at an atomic scale (12, 13). The incorporation of Fin FETs within the nano-scale domain has inaugurated a novel epoch in semiconductor innovation, underpinning the development of exceptionally efficient and highperformance integrated circuits that serve a diverse spectrum of applications – ranging from portable devices to cutting-edge computing systems (14, 15).

This research paper introduces a study focused on a symmetrical structural design involving a Fin Field-Effect Transistor (FIN-FET) as shown in section 2. Through advanced TCAD simulation techniques, the investigation delves into the intricate characteristics of the FIN-FET, exploring parameters like drain current, electric field distribution, surface potential variations, energy band configurations, carrier concentration behaviors, and the Ion/Ioff ratio as shown in section 3. The research sheds light on how this symmetrical design influences these fundamental aspects of the FIN-FET's operation. The insights gained hold the potential to refine device designs and optimize the application of FIN-FET technology in advanced semiconductor contexts. Additionally, the paper evaluates the impact of gate engineering, doping engineering, and work function engineering on the device's drain current, contributing to a comprehensive understanding of its performance under various aspects.

The High-k GAA-FinFET device has been widely adopted in modern semiconductor technology,

particularly in advanced integrated circuits. This proposed device offers better electrostatic control over the channel, resulting in improved performance compared to traditional planar transistors. This is crucial for achieving higher speed and lower power consumption in electronic devices. The three-dimensional FinFET design helps mitigate leakage current issues prevalent in smaller transistor sizes. This reduction in leakage current contributes to lower power consumption and improved energy efficiency. The manufacturing process for Fin FET is more complex compared to traditional planar transistors. This complexity can result in increased production costs and challenges in fabrication.

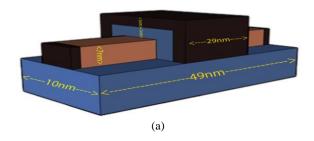

# 2. STRUCTURE OF PROPOSED DEVICE

The schematic view of the proposed device Fin-FET is shown in Figure 1. The 3-D ATLAS simulator is utilized to conduct device simulations. These parameters define the characteristics of the device under consideration. The gate length of 29 nm, fin thickness of 9 nm, and fin width of 10 nm determine the physical dimensions of the transistor. The channel thickness of 7 nm refers to the thickness of the conducting channel in the transistor. The gate oxide thickness (Tox) of 1 nm represents the thickness of the oxide layer between the gate and the channel (16-18). The source and drain length (Source and Drain) are both set at 10 nm. The source/drain doping 1x10^20 atoms/cm^3, indicating concentration of dopant atoms in the source and drain regions. The gate work function is 4.9 eV, signifying the energy level required to extract an electron from the gate and introduce it into the channel, influencing the transistor's behavior. These parameters collectively define the operational characteristics and behavior of the proposed device (19).

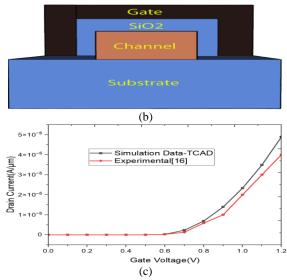

In the design and analysis of the Fin FET device, a comprehensive set of advanced simulation models has been employed to accurately capture its electrical and physical behavior (20, 21). The chosen models include Schrödinger-Poisson solver (Schro), Non-Equilibrium Green's Function with multisubband (NEGF\_MS), Oxide Schrödinger (Ox. Schro), semi-classical particle-based transport (sp. fast), and two-dimensional geometry representation (sp. geom=2dyz) as shown in Figure 2.

**Figure 1.** The structure of *the* proposed device (a) Dimensions of the device (b) Regions of the device (c) Calibrated Drain Currents

Figure 2. The Tentative Fabrication Process Flow of the proposed FinFET device

FinFET is designed in a three-dimensional structure, where the channel is a raised fin surrounded by the gate on all sides. This design allows for better electrostatic control of the channel and mitigates short-channel effects. In contrast, planar transistors have a two-dimensional structure, and as transistor sizes shrink, controlling the channel becomes more challenging. The three-dimensional FinFET design helps to reduce leakage current significantly. Leakage current is a critical concern in smaller transistor sizes due to increased quantum tunneling effects.

The parameters used for the simulation of the proposed device and performance parameters are shown in Table 1 and the comparison table is shown in Table 2.

# 3. RESULTS AND DISCUSSIONS

**3. 1. Gate Engineering** Modifying the gate thickness in FinFET devices has a significant impact on their performance characteristics. Specifically, - reducing the gate thickness plays a crucial role in enhancing the device's performance. Decreasing the gate thickness allows for better electrostatic control over the channel. This results in more precise regulation of the transistor's behavior. Thinning the gate effectively manages shortchannel effects, which can be a challenge in nanoscale transistors.

This improvement is critical for maintaining reliable transistor operation. The reduction in gate thickness increases gate capacitance. This increased capacitance provides greater control over the channel's behavior, enabling more effective gate regulation. Thinner gates lead to a decrease in the threshold voltage required for transistor activation. This is beneficial for achieving higher on-currents, which are essential for faster and more efficient transistor operation. Addressing concerns related to power leakage is a crucial aspect of modern semiconductor design. Thinner gates help in reducing power leakage, which is essential for energy-efficient device operation. Augmenting the gate thickness in Fin

**TABLE 1.** The dimensions of the proposed FinFET device

| Values |  |  |

|--------|--|--|

| 29 nm  |  |  |

| 9 nm   |  |  |

| 10 nm  |  |  |

| 7nm    |  |  |

| 1nm    |  |  |

| 10nm   |  |  |

| 10nm   |  |  |

| 1E20   |  |  |

| 9ev    |  |  |

|        |  |  |

**TABLE 2.** The comparison of the proposed Fin FET Device of its electric parameters with previous works

| Parameters | Proposed<br>Device | (9)                  | (22)                 | (23)                 |

|------------|--------------------|----------------------|----------------------|----------------------|

| Ion        | $5.79e^{-05}$      | 2.05e <sup>-05</sup> | 2.24e <sup>-05</sup> | 1.11e <sup>-05</sup> |

| Ioff       | $1.43e^{-18}$      | 5.2e <sup>-11</sup>  | 1.08e <sup>-11</sup> | 6.9e <sup>-13</sup>  |

| Ion/Ioff   | $4.05e^{+13}$      | $2.5e^{+06}$         | $1.85e^{+06}$        | $1.61e^{+07}$        |

| SS         | 55mV/D             |                      | 75 mV/D              | 61.97mV/D            |

FETs introduces divergent consequences. A thicker gate diminishes gate capacitance, introducing complexities in the effective modulation of the channel's conductance. While this adjustment could aid in reducing off-state leakage current, it could concurrently lead to sluggish switching speeds and sub-optimal electrostatic dominance over the channel (24).

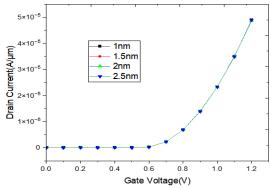

Figure 3 shows the variation in drain current for different gate thickness. A reduction in gate thickness brings about a notable increase in drain current. As such, the decision to manipulate the gate thickness necessitates meticulous consideration, weighing the desired trade-offs between performance, power efficiency, and switching speed. This evaluation should align with the distinctive application and design requisites of the FinFET device (25).

# 3. 2. Effect of Changing Doping Concentration

The doping concentration within FinFET structures yields significant changes in the drain current, revealing a direct correlation between doping levels and device performance. Elevated doping concentrations in the source and drain regions lead to an increased pool of charge carriers primed for conduction. This surplus of carriers translates into a higher drain current, facilitated by the amplified availability of charge carriers for seamless transport between the source and drain terminals. In contrast, reducing doping concentrations curtails the available carriers, subsequently diminishing the overall drain current. This controlled manipulation of

**Figure 3.** The Drain current characteristics of the proposed device for different gate thickness (1, 1.5, 2, 2.5nm)

The

doping concentration emerges as a potent strategy for tailoring the electrical traits of FinFETs. Through deliberate adjustments in doping levels, a fine equilibrium can be achieved, optimizing conduction efficiency while simultaneously curbing leakage currents. This dynamic tuning of doping concentration stands as a versatile approach for refining the performance characteristics of the device to meet specific application demands (26).

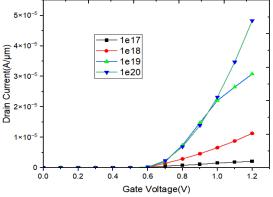

Figure 4, shows the variation in drain current for different doping concentrations. With a rise in doping concentration within the source and drain regions of FinFET structures, the abundance of available charge carriers for conduction experiences a significant surge. This excess of charge carriers plays a pivotal role in driving a substantial increase in the drain current. This augmentation is facilitated by the heightened availability of charge carriers, enabling efficient transportation between the source and drain terminals (27). Consequently, this heightened carrier concentration contributes to an elevated level of conductivity, thereby enhancing the overall performance of the device. By elevating the doping concentration, the device's suitability for facilitating current flow is enhanced, leading to an amplification of its capacity to manage electrical signals.

# 3. 3. Effect of Changing Work Functions

work function within the Fin FET framework across the range of 4.9 to 5.3 introduces noticeable alterations in the drain current, uncovering a direct correlation between work function values and the device's operational prowess. As the work function progressively increases from 4.9 to 5.3, a transformation occurs in the energy barrier situated at the gate-channel interface. This evolution in the energy barrier has a direct impact on how charge carriers respond to the gate voltage's influence—altering the balance between attraction and repulsion. With a higher work function, the energy barrier becomes narrower, facilitating a more efficient regulation of

**Figure 4.** The drain current for gate voltage for different doping concentration (1e17, 1e18, 1e19, 1e20)

charge carrier flow between the source and drain regions. This heightened gate control culminates in an amplified drain current, as charge carriers encounter reduced resistance during their traversal (28).

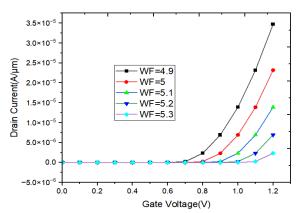

Figure 5 shows the relationship between drain current and gate voltage for varying work functions ranging from 4.9eV to 5.3eV in the FinFET device. As the work function increases, the modulation of drain current becomes more pronounced, highlighting the pivotal role of work function in influencing device behavior and performance (29).

# 3. 4. The Optimization of the Proposed Device

Incorporating modifications to the device based on the analysis of drain current, we have established fixed values for the gate thickness, doping concentration, and the work function of the gate metal. The parameters such as electric field, surface potential, energy bands, and carrier concentration have been analyzed for the suggested device.

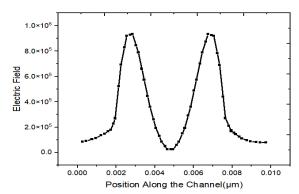

In Figure 6, we have observed the spatial profile of the electric field of this proposed device within the channel of a FinFET. Understanding the energy bands within a FinFET is pivotal for comprehending its electronic behavior.

**Figure 5.** The variation in drain current with respect to gate voltage for different work functions (4.9-5.3)

**Figure 6.** The electric field concerning position along the channel for the proposed device

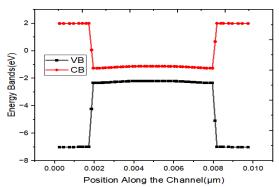

Figure 7 is a comprehensive visualization of the energy bands across the channel length within a Fin FET device. Consequently, this graphical representation enhances our understanding of the interplay between spatial positioning and energy distribution, a pivotal factor in shaping the device's overall performance characteristics.

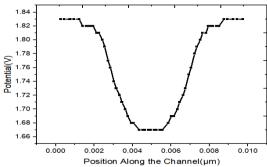

Figure 8 is a visual depiction that effectively showcases the distribution of potential across the length of the channel within a Fin FET device. This provides valuable insights into the progressive changes in potential as they relate to spatial position within the channel. Notably, the unique three-dimensional structure of the fin-like channel introduces intricate variations in potential along both the vertical and lateral dimensions.

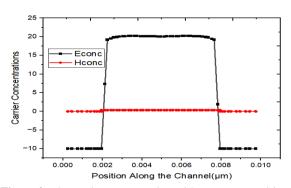

Figure 9 is a visual portrayal that offers insight into the alteration of carrier concentration across the channel's length within a Fin FET (Fin Field-Effect Transistor) device. This representation sheds light on the transformation of charge carrier density—whether electrons or holes—relative to the spatial location within the channel. The concentration undergoes subtle shifts as one traverses from the source to the drain region. The channel's distinct three-dimensional fin-like design introduces complex changes in carrier concentration, encompassing both vertical and lateral dimensions.

Figure 7. The energy bands concerning position along the channel for the proposed device

Figure 8. The potential concerning position along the channel for the proposed device

**Figure 9.** The carrier concentration with respect to position along the channel for the proposed device

# 4. CONCLUSION

This paper presents a comprehensive investigation into a symmetrical structural design centered around the Fin Field-Effect Transistor (Fin-FET). Through the utilization of advanced TCAD simulation techniques, the study delves deeply into the intricate characteristics of the Fin-FET, analyzing a wide array of crucial parameters such as drain current, electric field distribution, surface potential variations, energy band configurations, carrier concentration behaviors, and the Ion/Ioff ratio. The symmetrical design's impact on these fundamental operational aspects of the Fin-FET has been rigorously examined, providing valuable insights into its behavior. The findings of this research contribute significantly to our understanding of the Fin-FET's behavior and performance. These insights hold substantial promise for the advancement of semiconductor technology, as they can guide the development of refined designs and optimized utilization of Fin-FETs in advanced applications.

#### 5. REFERENCES

- Kumar ES, Kumar P S, Vignesh NA, Kanithan S. Design and Analysis of Junctionless FinFET with Gaussian Doped for Nonpolar Structure. Silicon. 2022:1-9. 10.1007/s12633-021-01626-y

- Gowthami Y, Balaji B, Srinivasa Rao K. Performance Analysis and Optimization of Asymmetric Front and Back Pi Gates with Dual Material in Gallium Nitride High Electron Mobility Transistor for Nano Electronics Application. International Journal of Engineering, Transactions A: Basics. 2023;36(7):1269-77. 10.5829/ije.2023.36.07a.08

- Radhamma E, Vemana Chary D, Krishnamurthy A, Venkatarami Reddy D, Sreenivasa Rao D, Gowthami Y, et al. Performance analysis of high-k dielectric heterojunction high electron mobility transistor for rf applications. International Journal of Engineering, Transactions C: Aspects. 2023;36(9):1652-8. 10.5829/ije.2023.36.09c.09

- Howldar S, Balaji B, Srinivasa Rao K. Design and Qualitative Analysis of Hetero Dielectric Tunnel Field Effect Transistor Device. International Journal of Engineering, Transactions C: Aspects. 2023;36(6):1129-35. 10.5829/ije.2023.36.06c.11

- Karimi G, Shirazi S. Ballistic (n, 0) Carbon Nanotube Field Effect Transistors\'IV Characteristics: A Comparison of n= 3a+ 1 and n= 3a+ 2. International Journal of Engineering, Transactions A: Basics. 2017;30(4):516-22. 10.5829/idosi.ije.2017.30.04a.09

- Dixit A, Gupta N. A compact model of gate capacitance in ballistic gate-all-around carbon nanotube field effect transistors. International Journal of Engineering, Transactions A: Basics. 2021;34(7):1718-24. 10.5829/IJE.2021.34.07A.16

- Prakash MD, Nelam BG, Ahmadsaidulu S, Navaneetha A, Panigrahy AK. Performance analysis of ion-sensitive field effect transistor with various oxide materials for biomedical applications. Silicon. 2021:1-11. 10.1007/s12633-021-01413-9

- Chakrabarty R, Roy S, Pathak T, Kumar Mandal N. Design of Area Efficient Single Bit Comparator Circuit using Quantum dot Cellular Automata and its Digital Logic Gates Realization. International Journal of Engineering. 2021;34(12):2672-8. 10.5829/ije.2021.34.12c.13

- Howldar S, Balaji B, Srinivasa Rao K. Design and Analysis of Hetero Dielectric Dual Material Gate Underlap Spacer Tunnel Field Effect Transistor. International Journal of Engineering, Transactions C: Aspects. 2023;36(12):2137-44. 10.5829/IJE.2023.36.12C.01

- Mehrabani AH, Fattah A, Rahimi E. Design and Simulation of a Novel Hetero-junction Bipolar Transistor with Gate-Controlled Current Gain. International Journal of Engineering, Transactions C: Aspects 2023;36(03):433. 10.5829/ije.2023.36.03c.01

- Prakash MD, Krsihna BV, Satyanarayana B, Vignesh NA, Panigrahy AK, Ahmadsaidulu S. A study of an ultrasensitive label free silicon nanowire FET biosensor for cardiac troponin I detection. Silicon. 2022;14(10):5683-90. 10.1007/s12633-021-01352-5

- Meriga C, Ponnuri R, Satyanarayana B, Gudivada A, Panigrahy A, Prakash M. A novel teeth junction less gate all around FET for improving electrical characteristics. Silicon. 2021.

- Rafiee A, Nickabadi S, Nobarian M, Tagimalek H, Khatami H. Experimental investigation joining al 5083 and high-density polyethylen by protrusion friction stir spot welding containing nanoparticles using taguchi method. International Journal of Engineering, Transactions C: Aspects. 2022;35(6):1144-53. 10.5829/ije.2022.35.06c.06

- Kumar S, Sahoo G. A random forest classifier based on genetic algorithm for cardiovascular diseases diagnosis (research note). International Journal of Engineering, Transactions B: Applications. 2017;30(11):1723-9. 10.5829/ije.2017.30.11b.13

- Kamal N, Singh J. A highly scalable junctionless FET leaky integrate-and-fire neuron for spiking neural networks. IEEE Transactions on Electron Devices. 2021;68(4):1633-8. 10.1109/TED.2021.3061036

- Im K-S, An SJ, Theodorou CG, Ghibaudo G, Cristoloveanu S, Lee J-H. Effect of gate structure on the trapping behavior of GaN junctionless FinFETs. IEEE Electron Device Letters. 2020;41(6):832-5. 10.1109/LED.2020.2991164

- Cadareanu P, Gaillardon P-E. A TCAD simulation study of threeindependent-gate field-effect transistors at the 10-nm node. IEEE Transactions on Electron Devices. 2021;68(8):4129-35. 10.1109/TED.2021.3089671

- Hu L, Lou H, Li W, Chang K-C, Lin X. Suppression of statistical variability in Junctionless FinFET using accumulation-mode and charge plasma structure. IEEE Transactions on Electron Devices. 2020;68(1):399-404. 10.1109/TED.2020.3040137

- Sehgal HD, Pratap Y, Gupta M, Kabra S. Performance analysis and optimization of under-gate dielectric modulated Junctionless FinFET biosensor. IEEE Sensors Journal. 2021;21(17):18897-904. 10.1109/JSEN.2021.3090263

- Jung S-G, Park E, Shin C, Yu H-Y. LER-induced random variation—immune effect of metal-interlayer—semiconductor source/drain structure on N-type Ge Junctionless FinFETs. IEEE Transactions on Electron Devices. 2021;68(3):1340-5. 10.1109/ TED.2021.3050031

- Sehgal HD, Pratap Y, Gupta M, Kabra S. Performance Investigation of Novel Pt/Pd-SiO 2 Junctionless FinFET as a High Sensitive Hydrogen Gas Sensor for Industrial Applications. IEEE Sensors Journal. 2021;21(12):13356-63. 10.1109/JSEN.2021.3067801

- Kumar M, Aditya K, Dixit A. A junctionless accumulation mode NC-FinFET gate underlap design for improved stability and selfheating reduction. IEEE Transactions on Electron Devices. 2020;67(8):3424-30. 10.1109/TED.2020.2997848

- Kumar PK, Balaji B, Rao KS. Design and analysis of asymmetrical low-k source side spacer halo doped nanowire metal oxide semiconductor field effect transistor. International Journal of Electrical and Computer Engineering (IJECE). 2023;13(3):3519-29. 10.11591/ijece.v13i3.pp3519-3529

- Gowthami Y, Balaji B, Rao KS. Design and Analysis of a Symmetrical Low-κ Source-Side Spacer Multi-gate Nanowire Device. Journal of Electronic Materials. 2023;52(4):2561-8. 10.1007/s11664-023-10217-z

- Manasawi D, Srinivasa Rao K. Design and Analysis of Charge Plasma Junction Less TFET Biosensing Applications. Transactions on Electrical and Electronic Materials. 2023;24(1):65-72. 10.1007/s42341-022-00419-3

- Harika P, Kondavitee GS, Rao KS, editors. Design and Analysis

of Dielectrically Modulated Tunnel FET Embedded Nanocavity

for BreastCancer Cells. 2023 IEEE Devices for Integrated Circuit

(DevIC); 2023: IEEE. 10.1109/DevIC57758.2023.10134925

- Fouladinia F, Gholami M. Decimal to excess-3 and excess-3 to decimal code converters in QCA nanotechnology. International Journal of Engineering, Transactions C: Aspects. 2023;36(9):1618-25. 10.5829/ije.2023.36.09c.05

- Balaji B, Sravani SS, Rao KS. Qualitative Analysis of DG-TFET Structures with Gate material Engineering. Journal of Integrated Circuits and Systems. 2022;17(3):1-6. 10.29292/jics.v17i3.635

- Balaji B, Srinivasa Rao K, Girija Sravani K, Bindu Madhav N, Chandrahas K, Jaswanth B. Improved drain current characteristics of hfo2/sio2 dual material dual gate extension on drain side-tfet. Silicon. 2022;14(18):12567-72. 10.1007/s12633-022-01955-6

# **COPYRIGHTS**

©2024 The author(s). This is an open access article distributed under the terms of the Creative Commons Attribution (CC BY 4.0), which permits unrestricted use, distribution, and reproduction in any medium, as long as the original authors and source are cited. No permission is required from the authors or the publishers.

# Persian Abstract

#### چکیده

این مقاله یک طراحی ساختاری متقارن را با محوریت ترانزیستور اثر میدانی باله نانومقیاس (Fin-FET) معرفی و بررسی می کند. این مطالعه با استفاده از تکنیکهای شبیه سازی tcad پیشرفته، ویژگیهای Fin-FET را مورد بحث قرار می دهد. در اینجا، یک کاوش جامع از عملکرد دستگاه در طیفی از پارامترها، از جمله جریان تخلیه، توزیع میدان الکتریکی، تغییرات پتانسیل سطحی، پیکربندی های باند انرژی، رفتارهای غلظت حامل و نسبت یون / یون است. از طریق تجزیه و تحلیل دقیق، این تحقیق تأثیر طراحی متقارن را بر این جنبه های اساسی عملکرد Fin-FET روشن می کند. بینشهای به دست آمده از این مطالعه، پتانسیل افزایش درک ما از رفتار دستگاه، هموار کردن راه را برای طراحیهای دقیق و استفاده بهینه از فناوری Fin-FET در کاربردهای نیمه رسانای پیشرفته دارد. چندین نوع مهندسی برای آزمایش دستگاه در جنبه های مختلف اعمال می شود. مهندسی گیت، مهندسی دوپینگ و مهندسی عملکرد کار برای آزمایش ویژگیهای جریان تخلیه دستگاه استفاده شد. بنابراین، این پیشنهاد به طور گسترده ای در دستگاه های نیمه هادی در مقیاس نانو مدرن پذیرفته شده است.